Kraklog

[Vivado] 2x4 Decoder , 7-Segment 본문

사용프로그램 : Vivado

사용보드 : BASYS 3

-BASYS3 보드를 선택하기위해서 VIVADO에서 보드 정보를 INSTALL해주면 되지만, 간혹 INSTALL 버튼이 없을 경우 직접 설치하면 되는데 C:\Xilinx\Vivado\(해당버전)\data\boards path에 보드 파일(링크)을 넣어주면 된다.

1. 2x4 Decoder

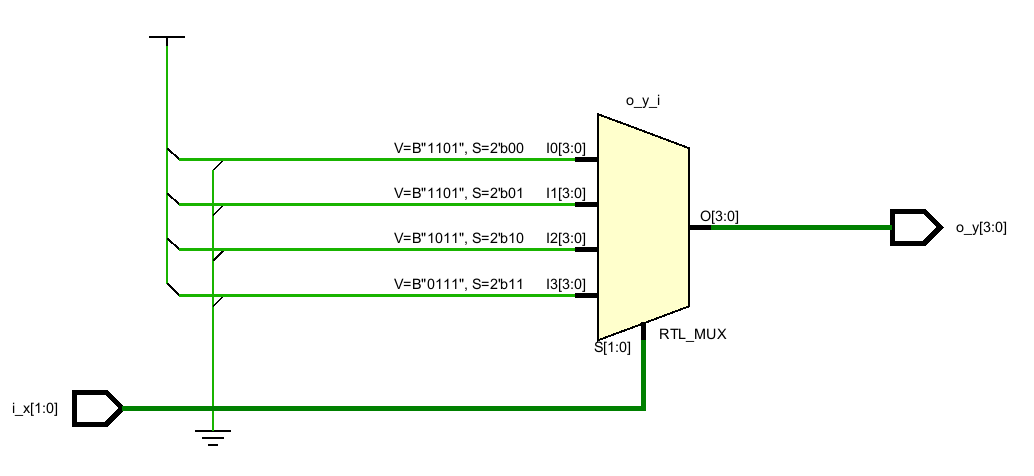

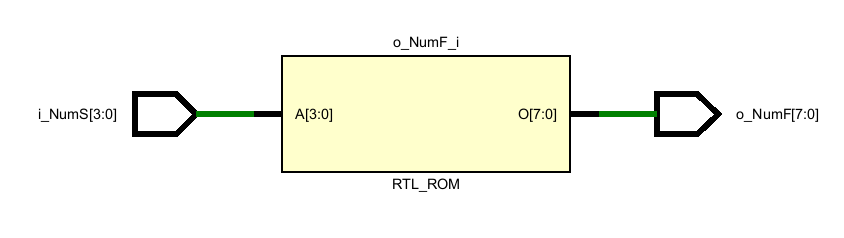

- Schematic

디코더는 n 비트의 2진코드를 최대 2의 n승개의 다른 정보로 바꾸어주는 조합 논리회로이다.

즉, A B와 같이 2개의 입력이 들어오면 4개의 출력을 내보낸다.

디코더를 설계하기 위해서, input을 [1:0]으로 잡아주고, output을 [3:0]으로 잡아 2x4 구조를 만들어주고

각 입력값에 따른 출력을 할당해주어 디코더를 설계해보려 한다.

- Code

`timescale 1ns / 1ps

module decoder_2x4(

input [1:0] i_x ,

output reg [3:0]o_y

);

always @(*) begin

case (i_x)

2'b00 : o_y = 4'b1110 ;

2'b01 : o_y = 4'b1101 ;

2'b10 : o_y = 4'b1011 ;

2'b11 : o_y = 4'b0111 ;

default: o_y = 4'b0000;

endcase

end

endmodule- 검증

2. 7-Segment (FND)

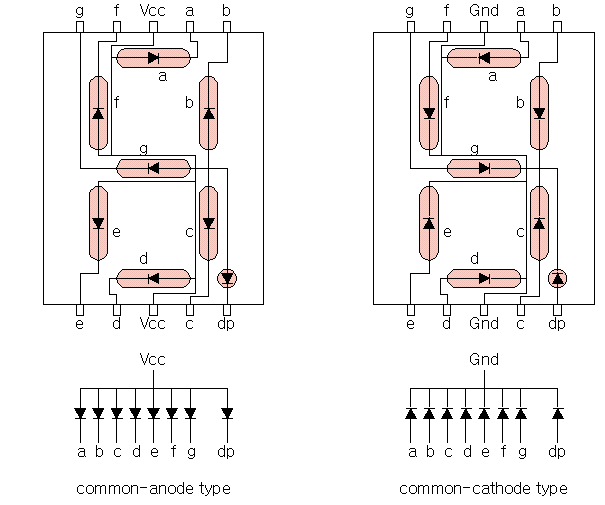

7-Segment는 Common-Anode type과 Common-Cathode type로 나뉜다.

LED (Light Emitting Diode) 는 다이오드의 일종으로 전류의 방향성을 갖는다.

또한 옴의 법칙에 의해 고정된 저항과 VCC, GND의 방향을 안다면 전류의 방향을 알 수 있다.

따라서 7-Segment가 Common Annode type (공통 양극) 이라면 코딩 혹은 핀에 1 혹은 전압을 가해준다면 전류가 흐르지 않기 때문에 LED의 빛이 들어오지 않게 된다. Common Cathode typed의 경우 그와 반대가 된다.

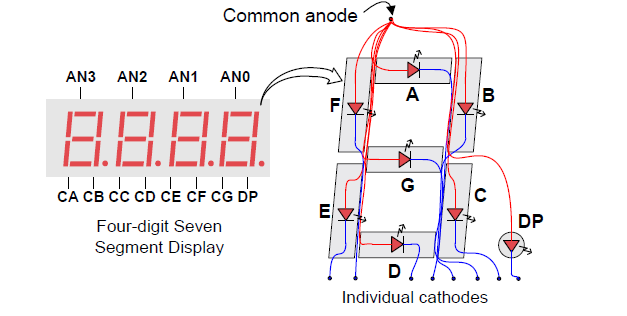

Datasheet 상 Basys3의 segment는 위와 같기 때문에, 이를 고려해서 FND를 조절 할 수 있는 코드를 빌드하는데

출력부분 할당에는 8'b 0000_0000 을 해주는데 각자리별 순서는 8'b DP G F E _ D C B A 로 지정된다.

또한 FND가 4개가 있기 때문에, input [3:0] 값을 주어 자릿수를 선택할 수 있게 해준다.

- Code

`timescale 1ns / 1ps

module FND_Cntrl(

input [3:0] i_NumS ,

output reg [7:0] o_NumF

);

always @ (*) begin

case (i_NumS) //8'b dp g f e _ d c b a

4'd0 : o_NumF = 8'b1100_0000;//8'hc0

4'd1 : o_NumF = 8'b1111_1001;//8'hf9

4'd2 : o_NumF = 8'b1010_0100;//8'ha4

4'd3 : o_NumF = 8'b1011_0000;//8'hb0

4'd4 : o_NumF = 8'b1001_1001;//8'h99

4'd5 : o_NumF = 8'b1001_0010;//8'h92

4'd6 : o_NumF = 8'b1000_0010;//8'h82

4'd7 : o_NumF = 8'b1111_1000;//8'hf8

4'd8 : o_NumF = 8'b1000_0000;//8'h80

4'd8 : o_NumF = 8'b1001_1000;//8'h99

default : o_NumF = 8'b1111_1111;//8'hf

endcase

end

endmodule- 검증

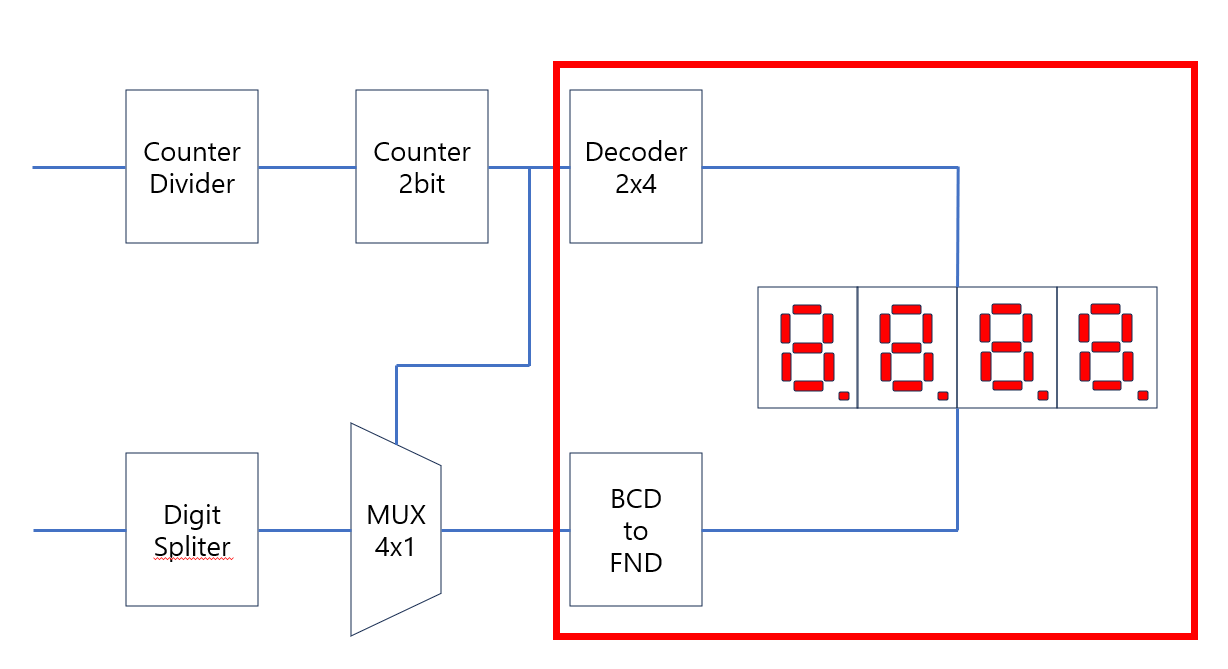

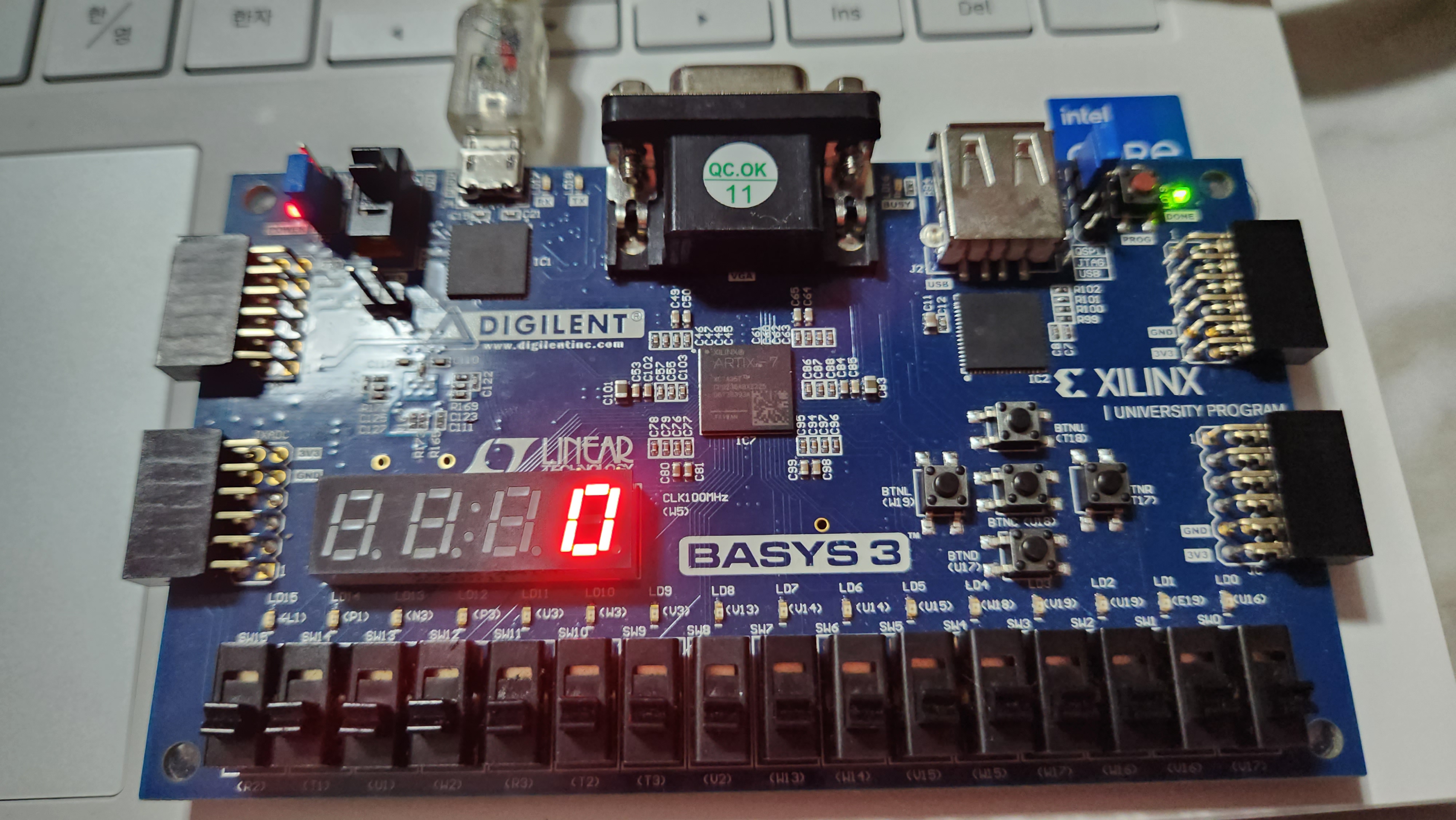

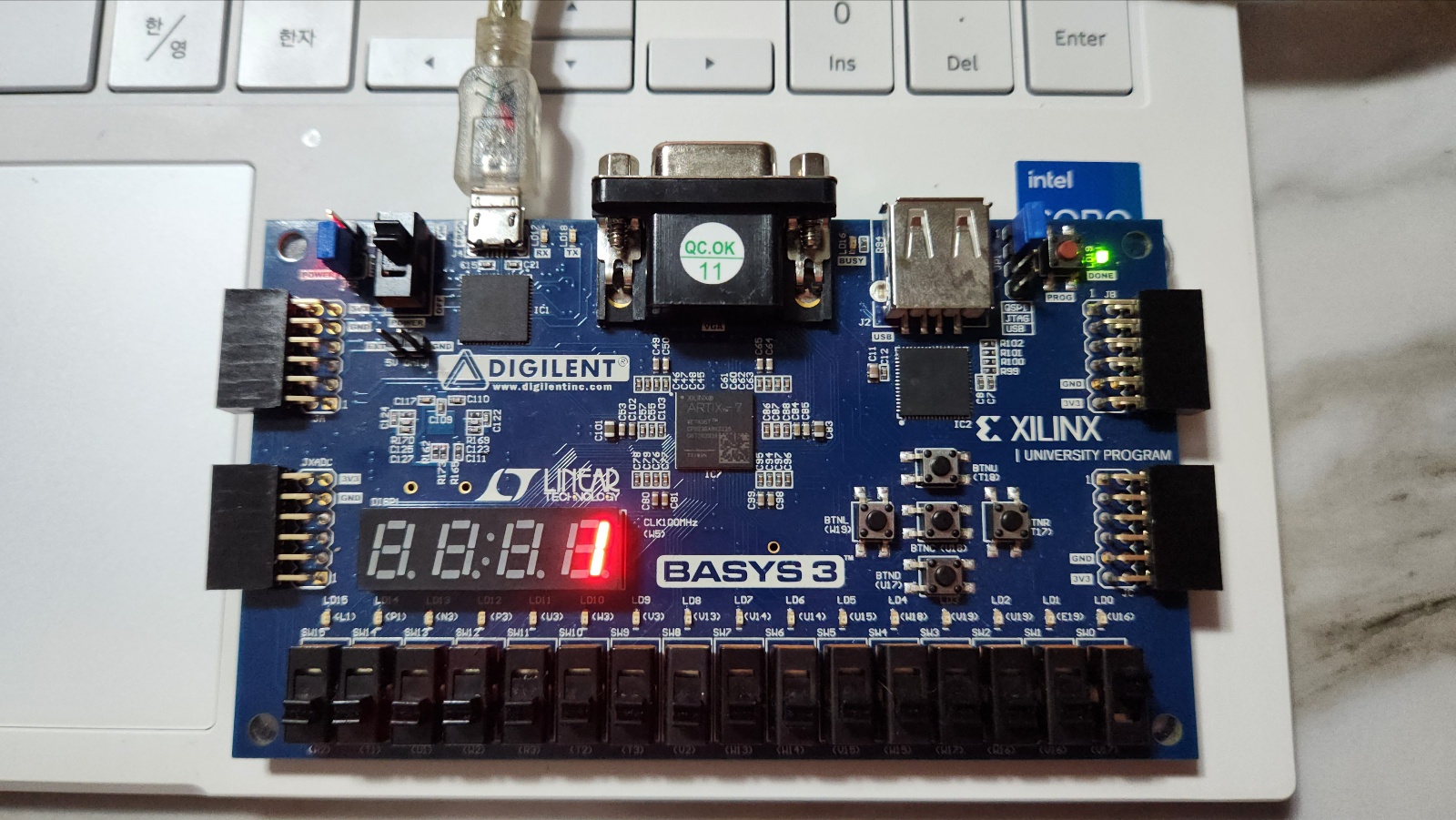

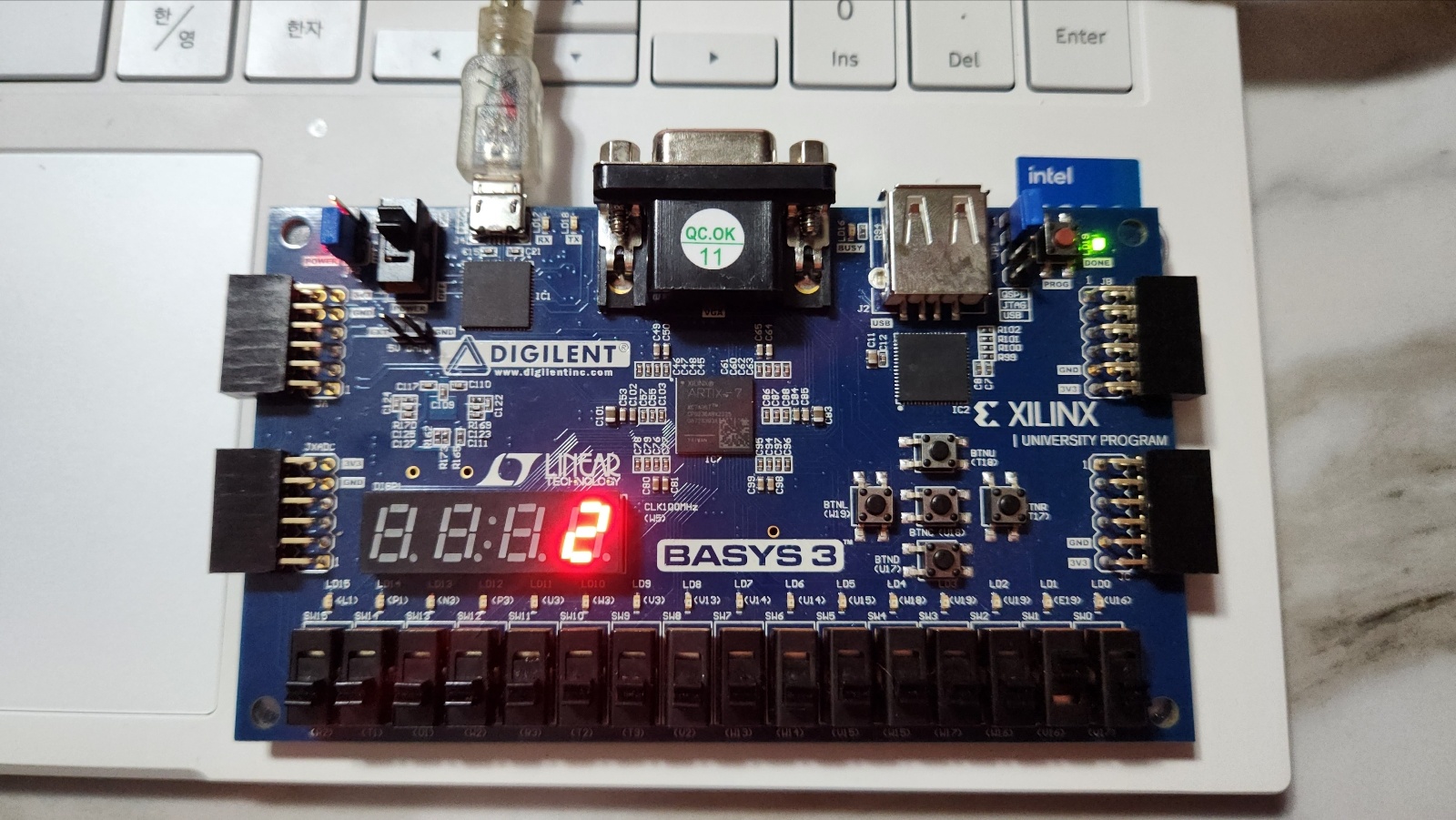

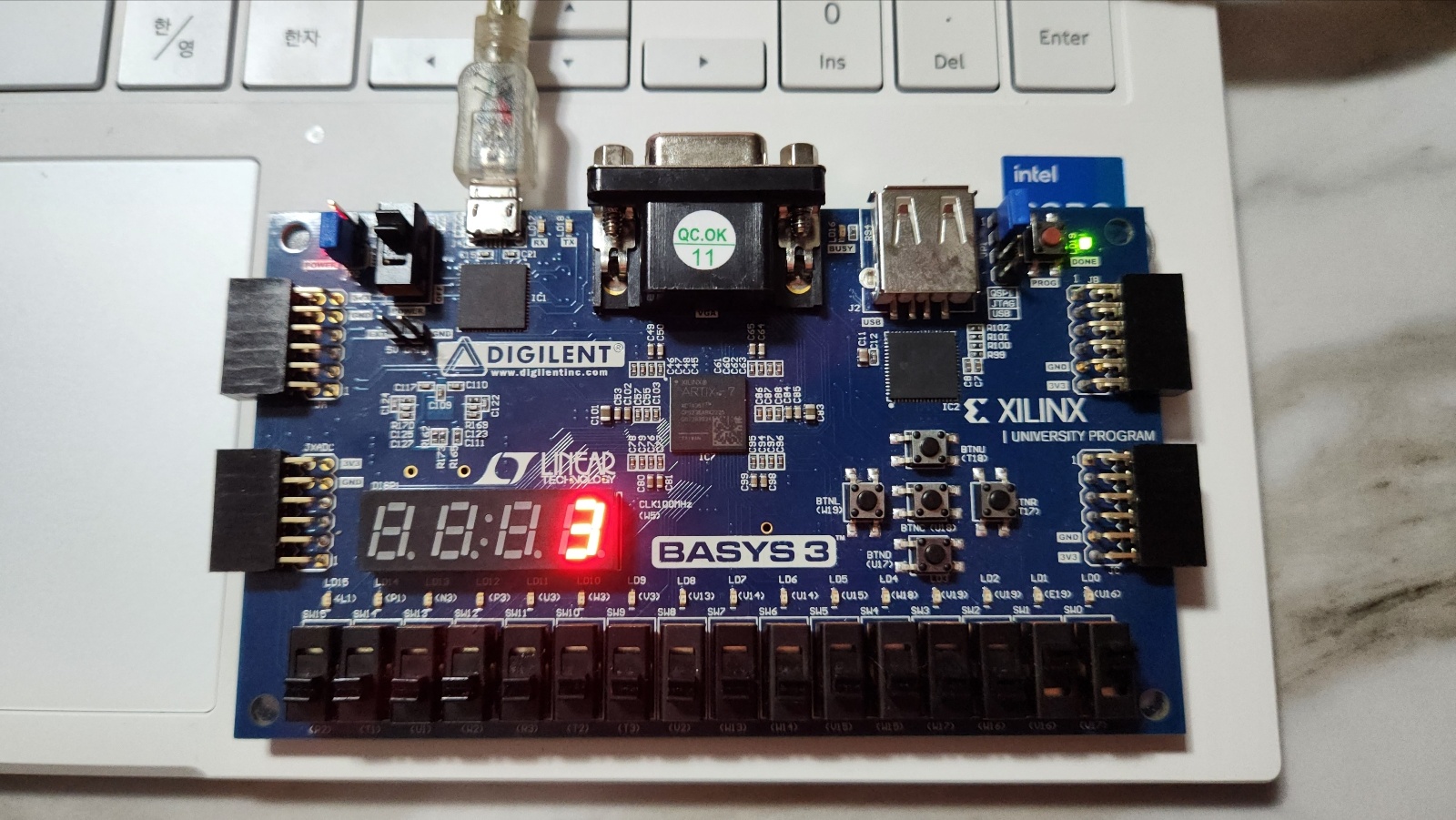

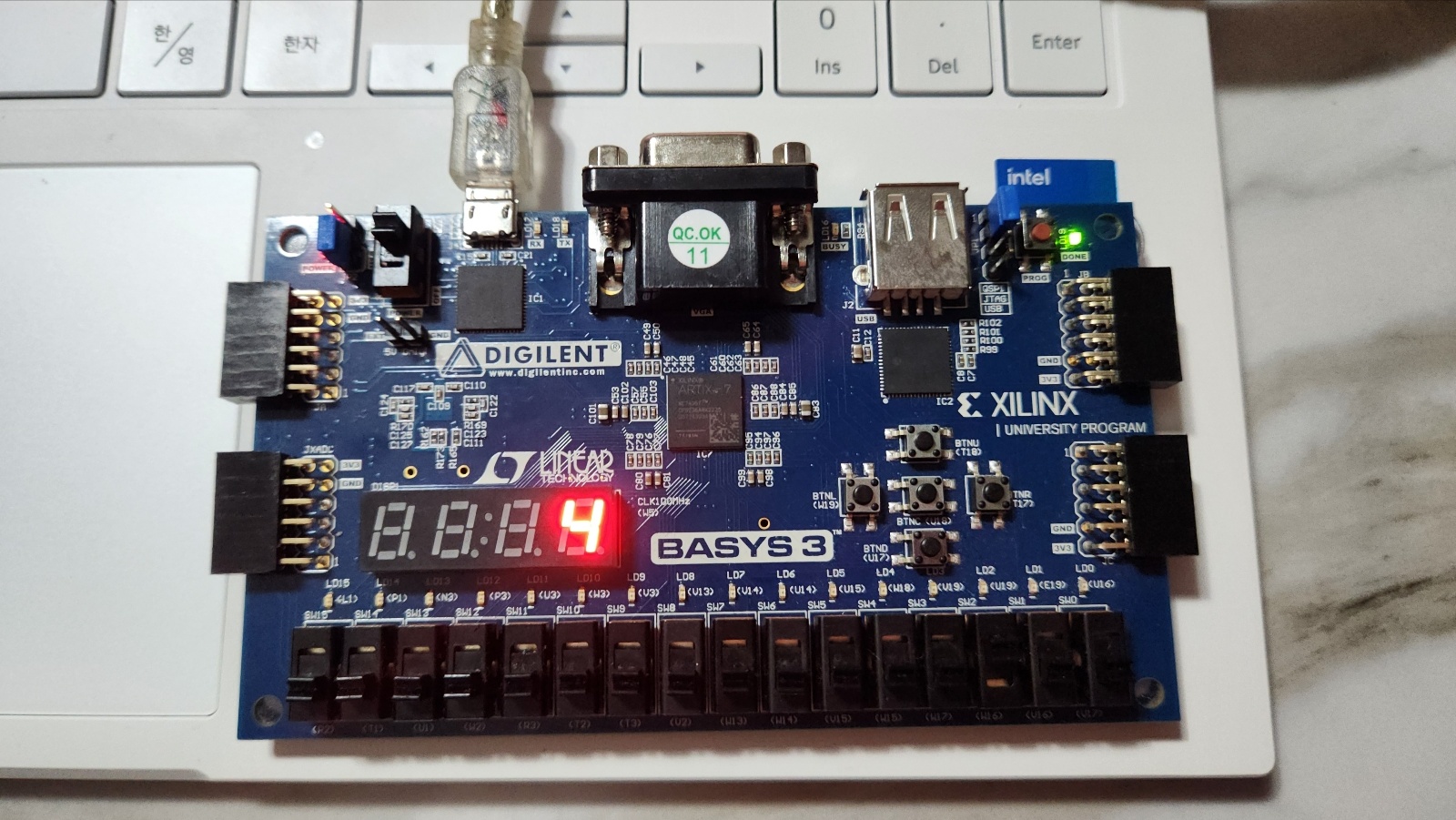

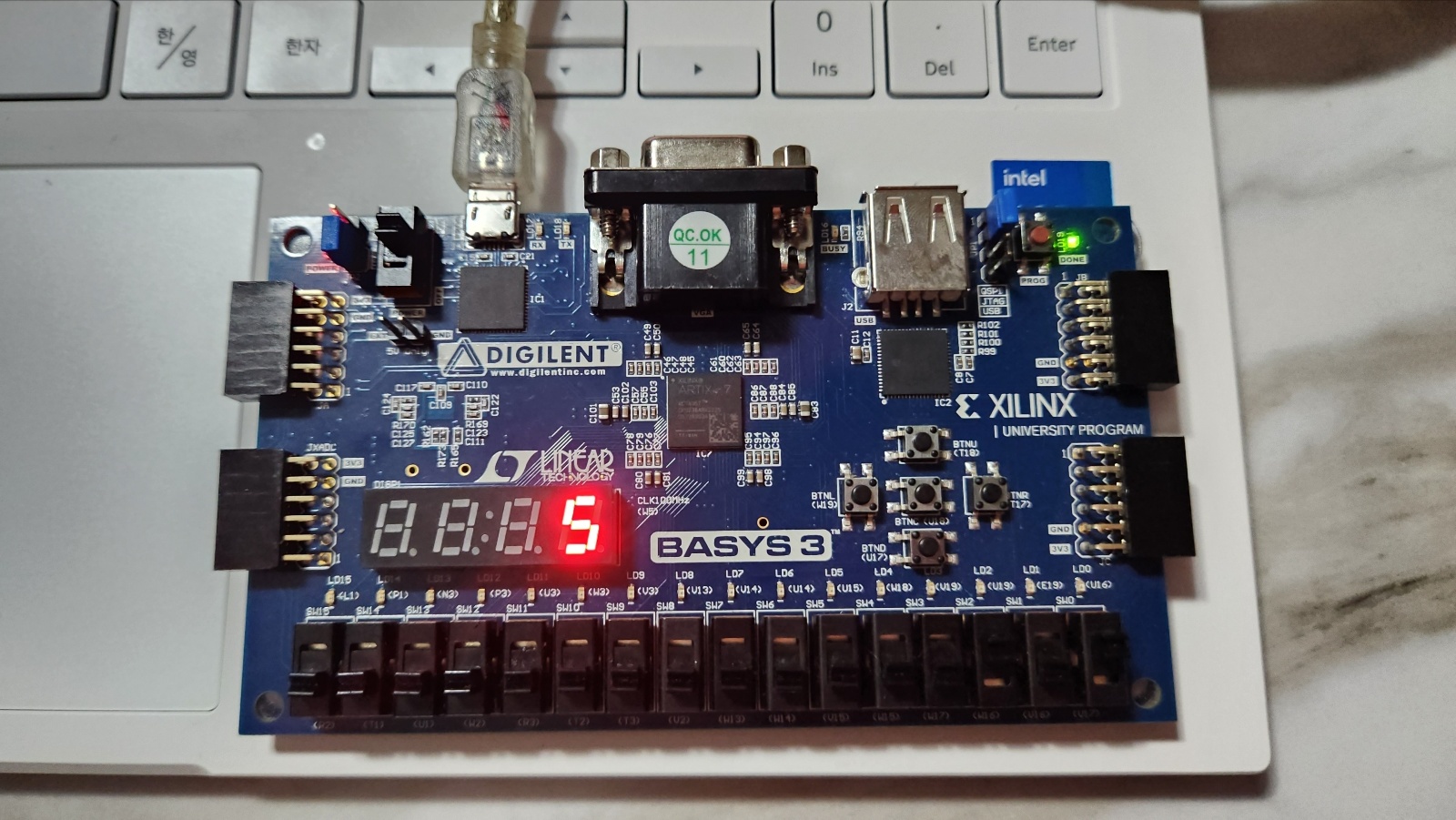

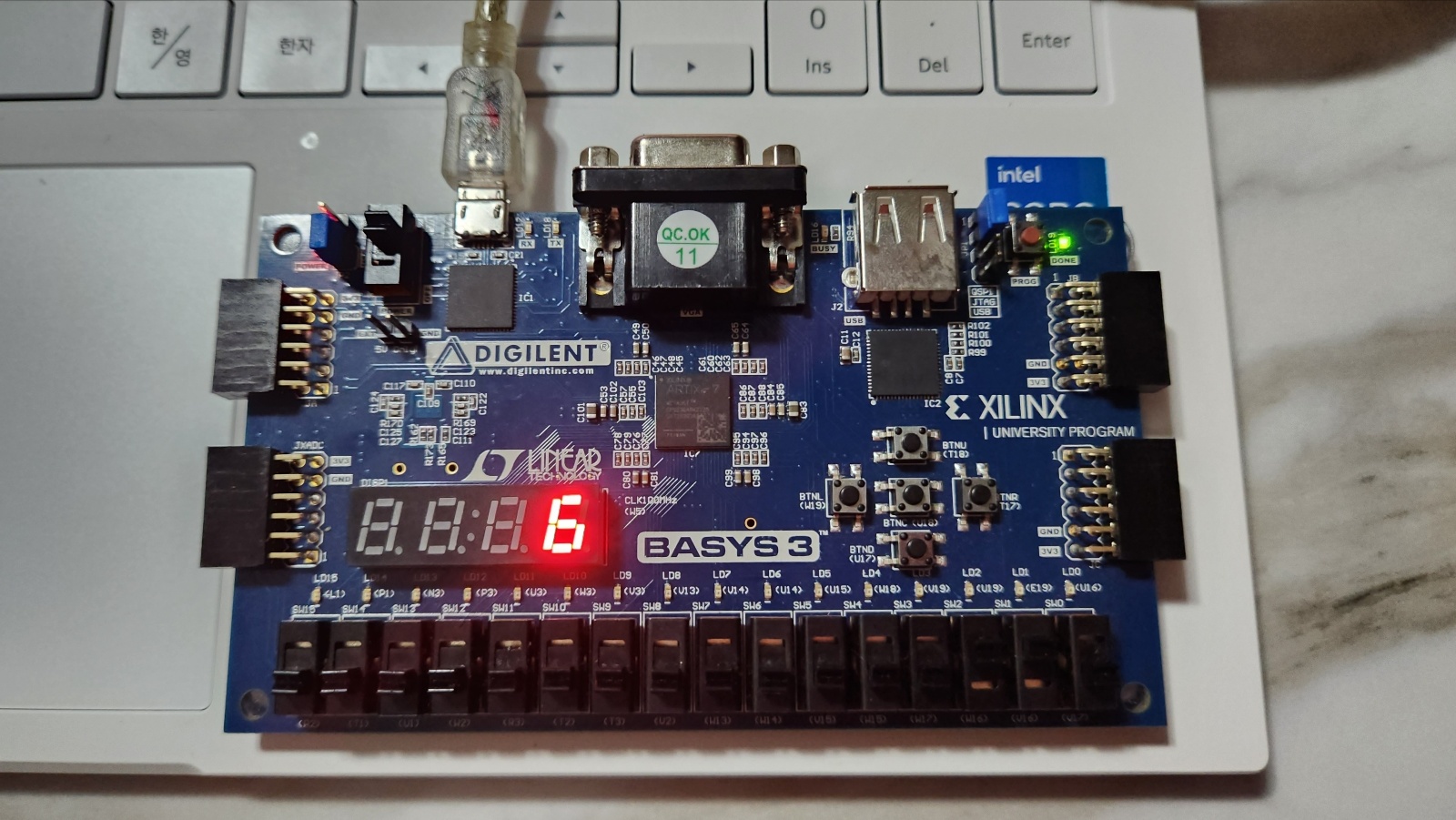

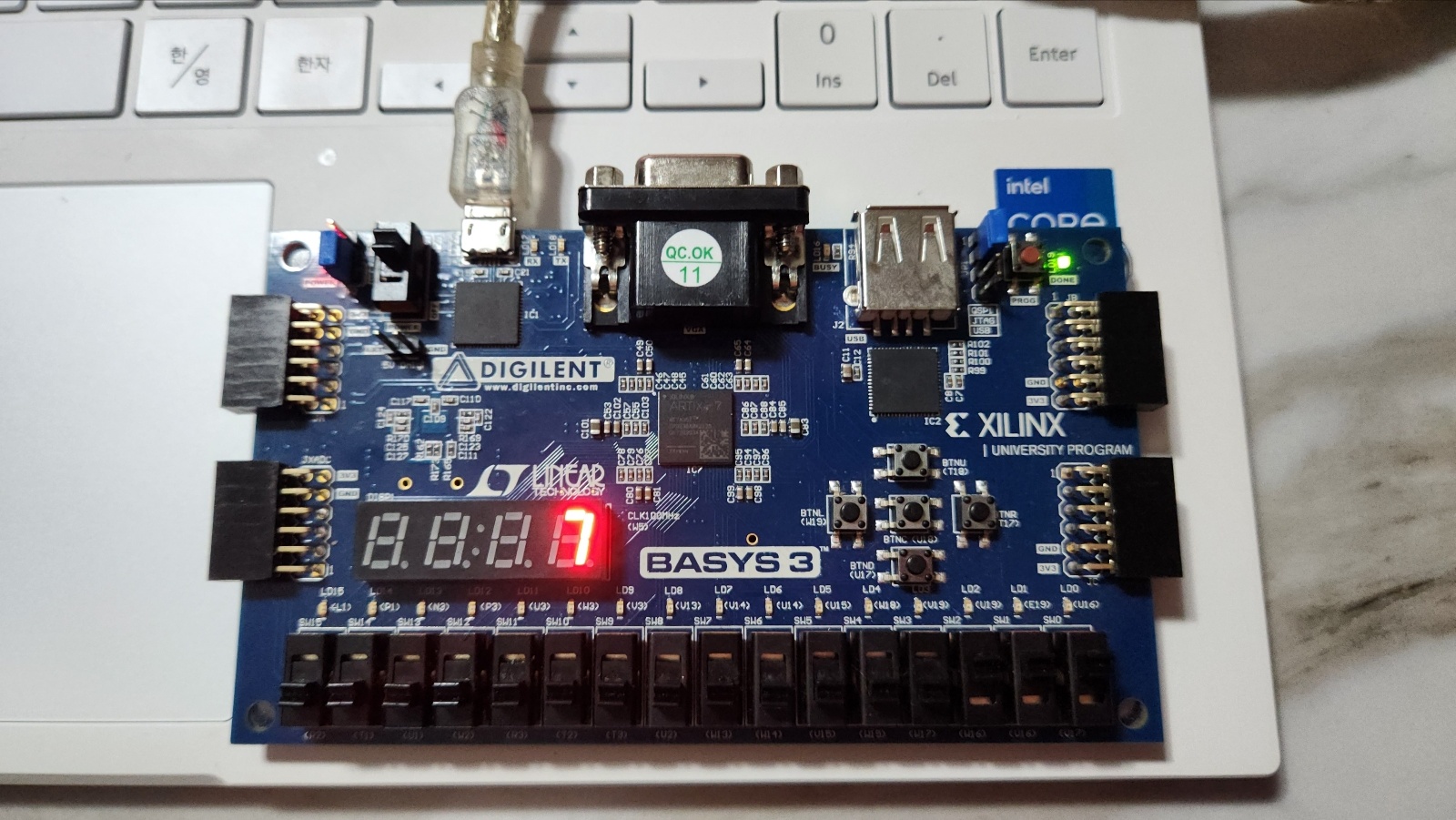

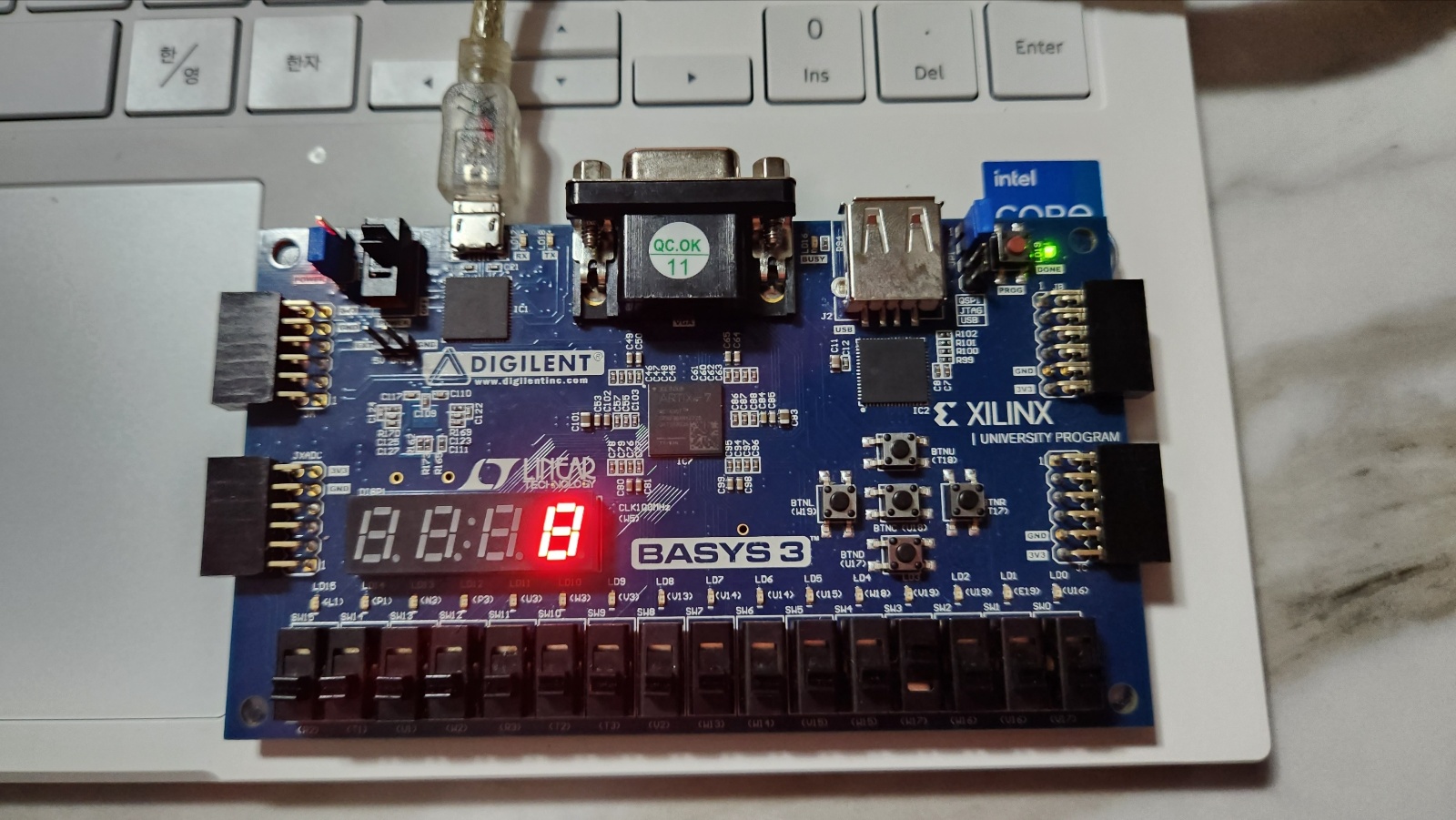

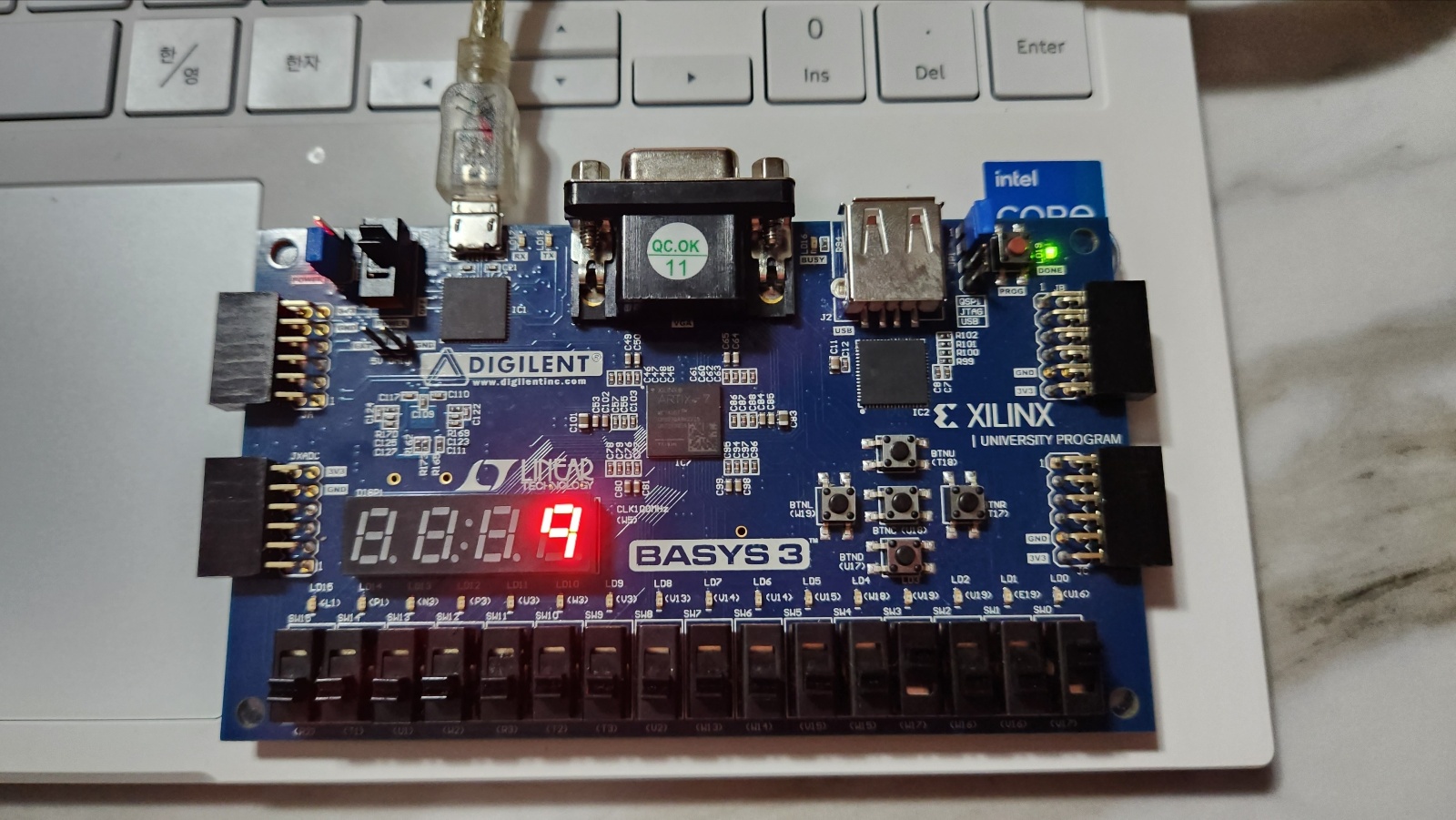

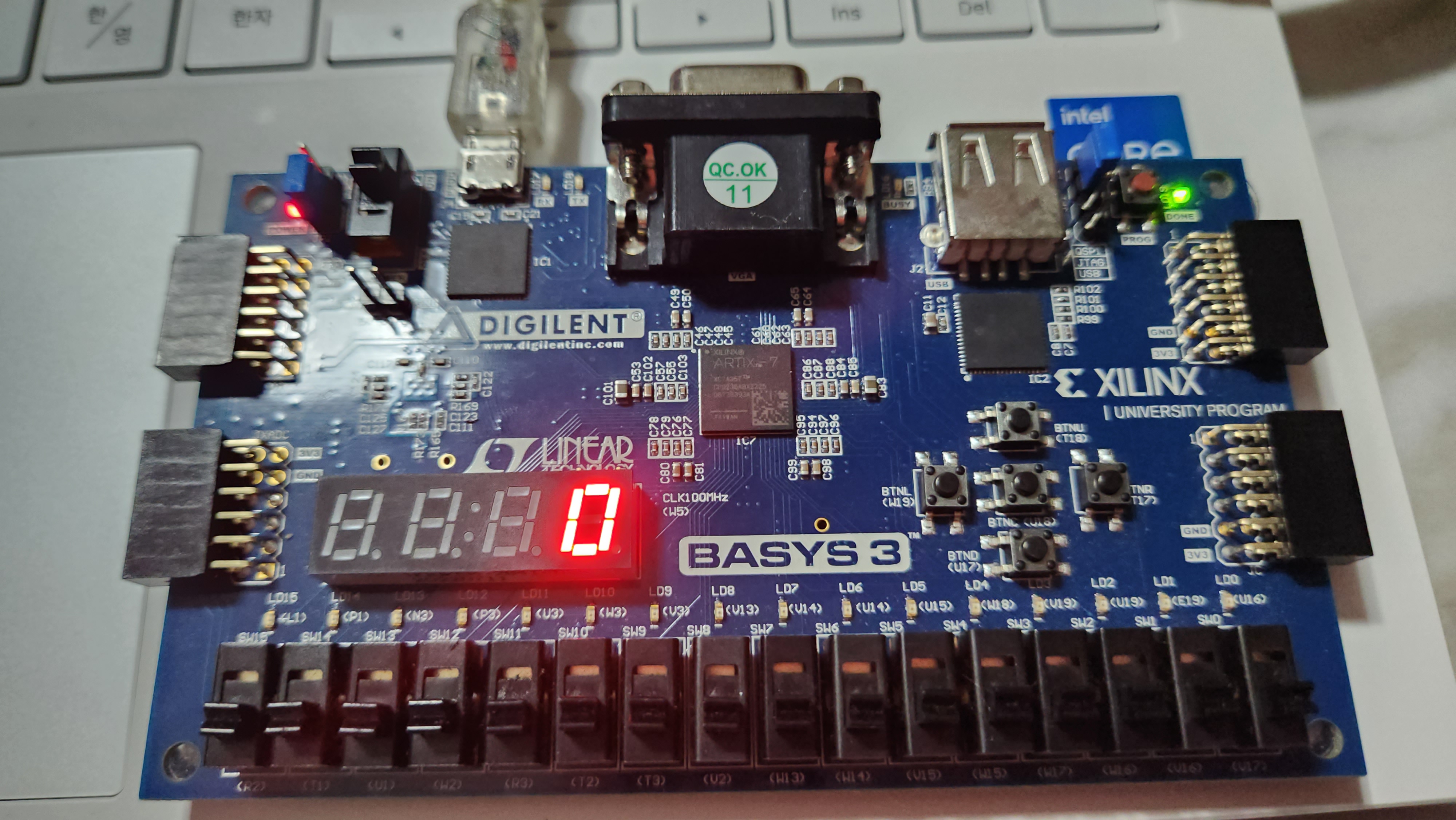

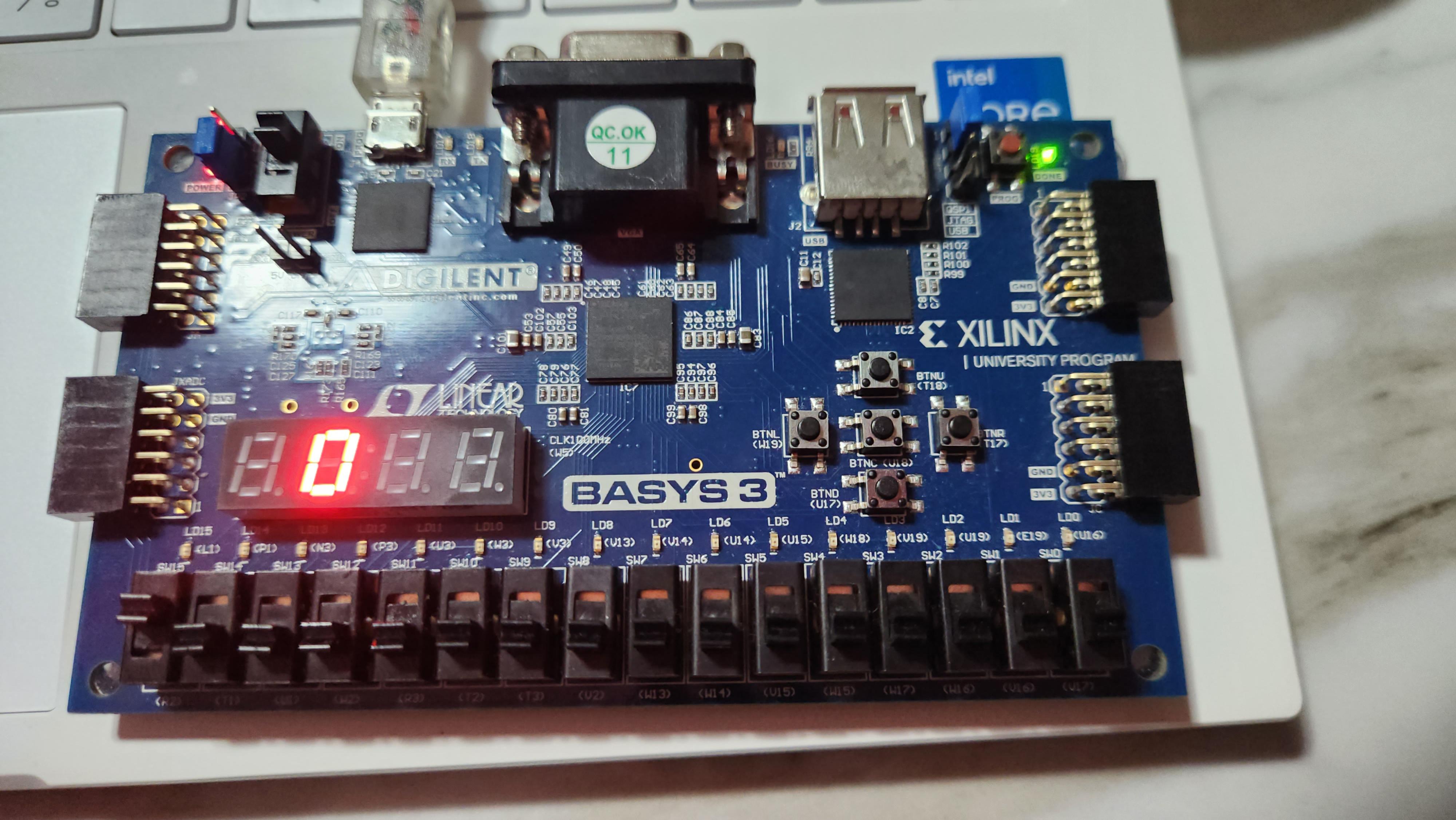

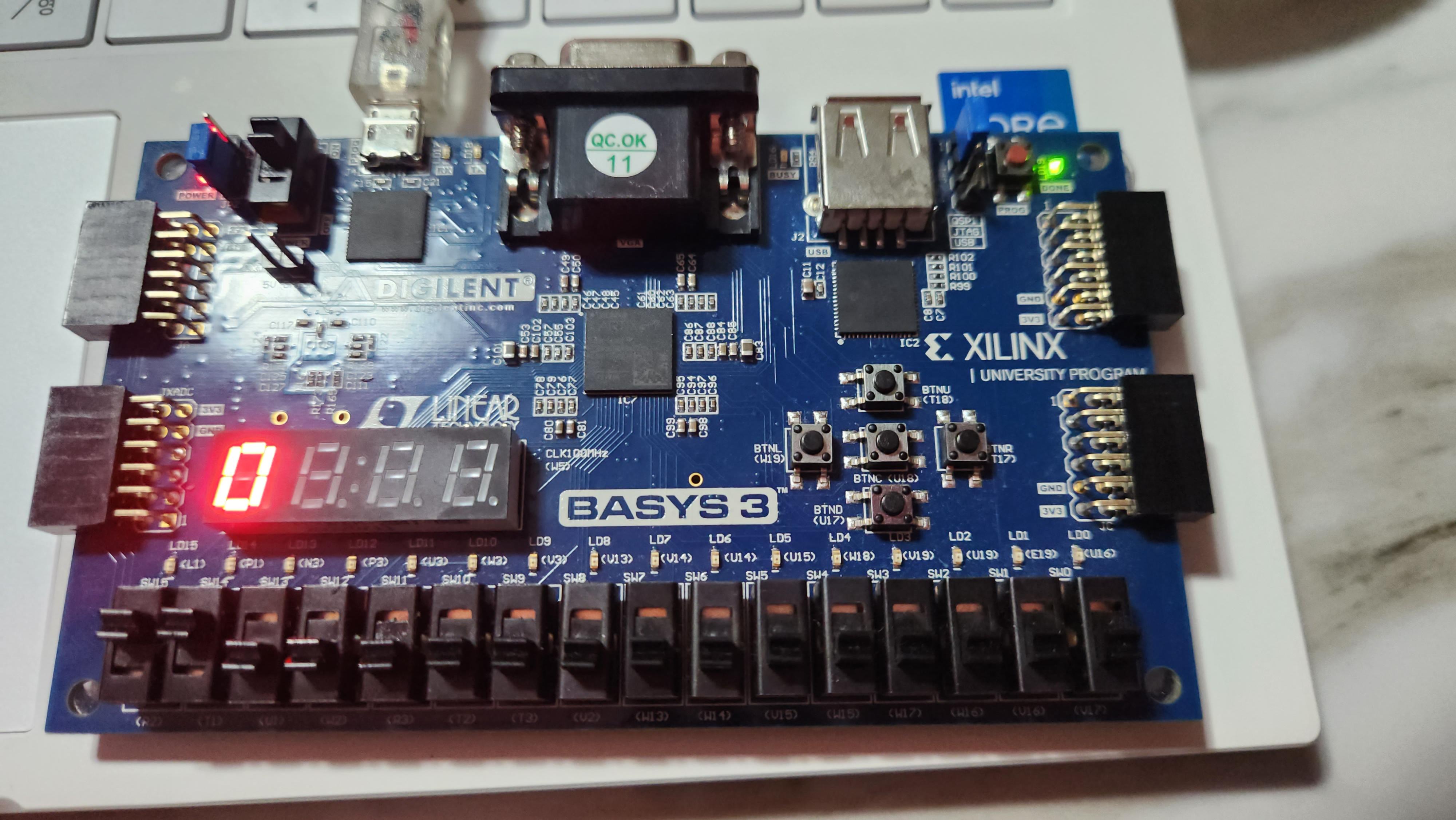

- 실습

현재 실습방향은 다음과 같으며, 빨간색 사각 박스까지 실습을 진행하였다.

가장 좌측 스위치 2개로 자릿수를 선택, 가장 우측 스위치를 이용해 9까지 숫자를 올려보았다.

'Study > VerilogHDL' 카테고리의 다른 글

| [Vivado] FSM (Stop Watch, 가산기) with button. (0) | 2023.08.04 |

|---|---|

| 레지스터와 카운터 (0) | 2023.08.04 |

| [Vivado] FSM (Stop Watch, 가산기) (0) | 2023.08.04 |

| [Vivado] 2 bit Counter, 4x1 Mux, Clock Divider (0) | 2023.08.02 |

| [Vivado] Adder (Half, 1bit Full, 4bit Full, 8bit Full) (0) | 2023.08.02 |