Kraklog

[Vivado] Adder (Half, 1bit Full, 4bit Full, 8bit Full) 본문

사용프로그램 : Vivado

사용보드 : BASYS 3

-BASYS3 보드를 선택하기위해서 VIVADO에서 보드 정보를 INSTALL해주면 되지만, 간혹 INSTALL 버튼이 없을 경우 직접 설치하면 되는데 C:\Xilinx\Vivado\(해당버전)\data\boards path에 보드 파일(링크)을 넣어주면 된다.

1. Half Adder

- Layout 및 시뮬레이션 (링크)

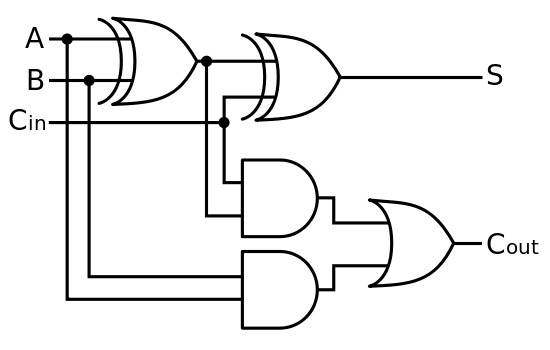

식 :

- Schematic

input으로 A,B를 선언해주고, Sum을 처리하기 위해 A xor B를 할당해주고, Carry 를 처리하기 위해 A and B를 할당해준다.

출력 값으로 Sum과 Carry를 선언해주면 완료.

- Code

`timescale 1ns/1ps

module HalfAdder (

input i_a,

input i_b,

output o_Sum,

output o_Crry

);

assign o_Sum = i_a ^ i_b; //A xor B

assign o_Crry = i_a & i_b; // A and B

endmodule-검증

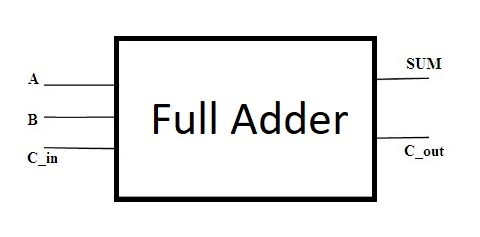

2. Full Adder (1bit Full Adder)

- Layout 및 시뮬레이션 (링크)

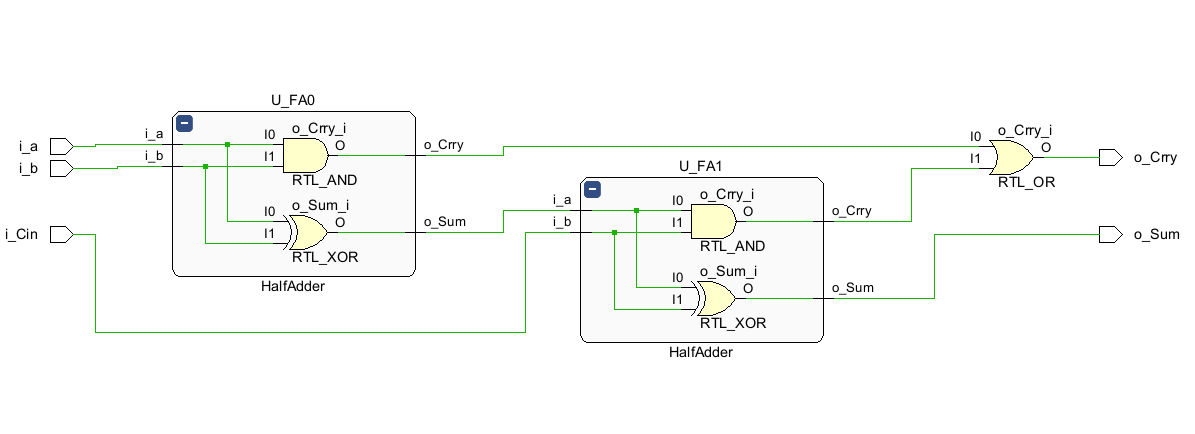

- Schematic

input으로 A,B,C_in을 선언해준다, Diagram에서 확인 가능하듯이 자릿수가 반영되므로 Cin이 할당이 되며,

wire 선언을 통해서 Half Adder 사이에 값을 입력시키면 될 것이며, Sum 값을 출력해주고,

Carry를 출력하기 위해서 OR 연산을 해주어 출력 값을 할당해준다.

- Code

`timescale 1ns / 1ps

module FullAdder_1bit(

input i_a,

input i_b,

input i_Cin,

output o_Sum,

output o_Crry

);

wire w_sum0,w_carry0,w_carry1;

HalfAdder U_HA0 ( //HalfAdder를 불러와 HA0 모듈로 지칭

.i_a(i_a),

.i_b(i_b),

.o_Sum(w_sum0),

.o_Crry(w_carry0)

);

HalfAdder U_HA1 (

.i_a(w_sum0),

.i_b(i_Cin),

.o_Sum(o_Sum),

.o_Crry(w_carry1)

);

assign o_Crry = w_carry0 | w_carry1;

endmodule-검증

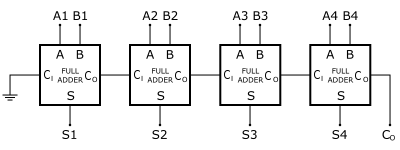

3. Full Adder (4bit Full Adder)

- Layout 및 시뮬레이션 (링크)

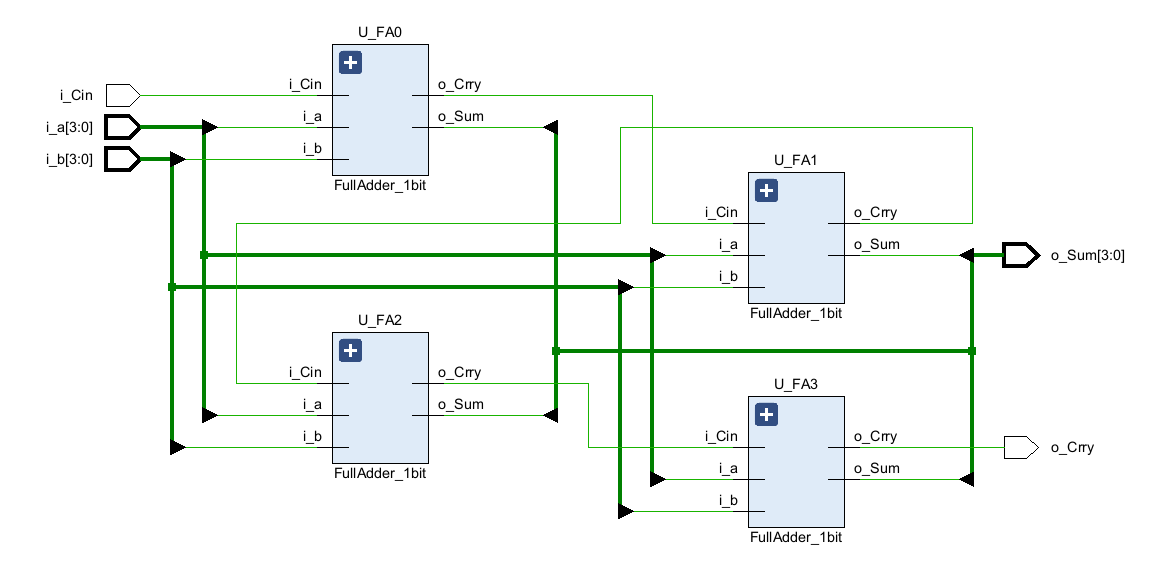

- Schematic

순서는 위 사진과는 다르겠지만 다음과 같이 구현하기위해서 wire를 통해 연결을 해주고,

할당해주면 출력이 나올것으로 보인다.

그러기 위해서 input 값을 [3:0]의 값으로 a,b에 할당해주고,

- Code

`timescale 1ns / 1ps

module FullAdder_4bit(

input [3:0] i_a,i_b,

input i_Cin,

output [3:0] o_Sum,

output o_Crry

);

wire w_carry0,w_carry1,w_carry2;

FullAdder_1bit U_FA0(

.i_a(i_a[0]),

.i_b(i_b[0]),

.i_Cin(i_Cin),

.o_Crry(w_carry0),

.o_Sum(o_Sum[0])

);

FullAdder_1bit U_FA1(

.i_a(i_a[1]),

.i_b(i_b[1]),

.i_Cin(w_carry0),

.o_Crry(w_carry1),

.o_Sum(o_Sum[1])

);

FullAdder_1bit U_FA2(

.i_a(i_a[2]),

.i_b(i_b[2]),

.i_Cin(w_carry1),

.o_Crry(w_carry2),

.o_Sum(o_Sum[2])

);

FullAdder_1bit U_FA3(

.i_a(i_a[3]),

.i_b(i_b[3]),

.i_Cin(w_carry2),

.o_Crry(o_Crry),

.o_Sum(o_Sum[3])

);

endmodule- 검증

4. Full Adder (8bit Full Adder)

- Layout 및 시뮬레이션 (링크)

- Schematic

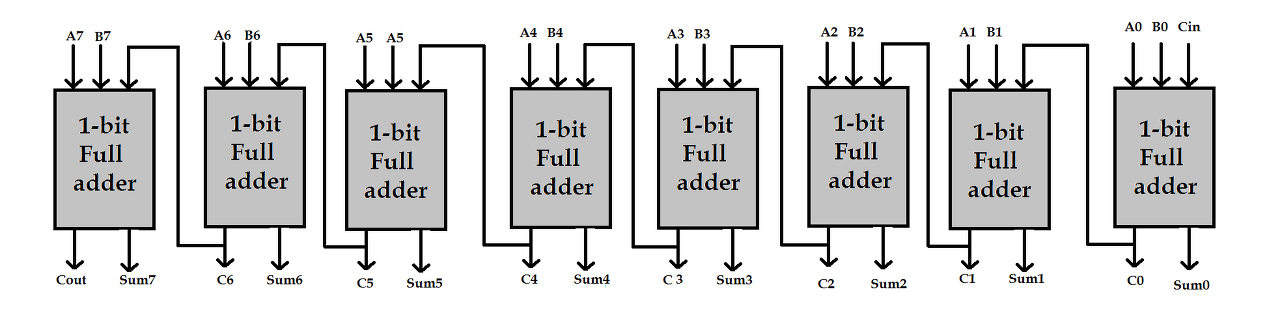

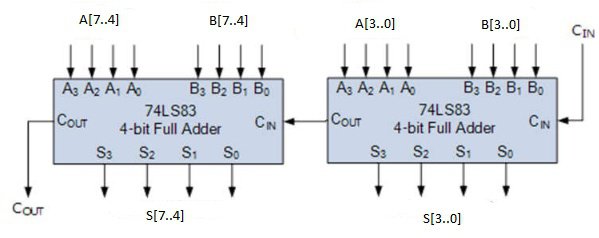

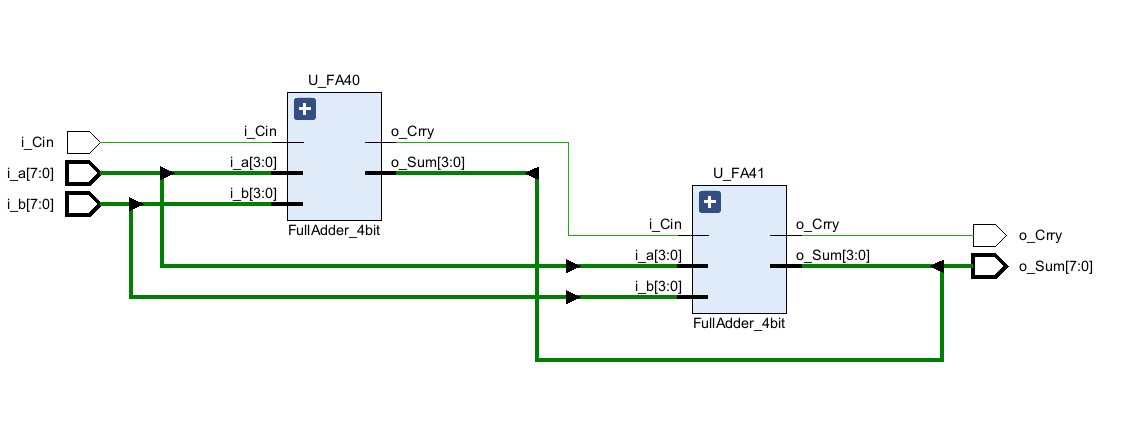

8bit Full Adder는 1bit Full Adder를 8개로 만들어 사용하거나, 만들어진 4bit Full Adder를 사용하는 방법이 있다.

결국 같은 방법이지만, 코드의 직관성과 편의성을 위해 4bit Full Adder를 2개를 사용할 예정이며,

이 때 wire 선언을 통해 Carry 값을 다음 4bit Full Adder에 연결을 통해 출력값을 받아낼 예정이다.

이렇게 하는 경우, 1bit로만 구성을 하면 4bit 처럼 .i_a[0] ~ i_a [7] 식으로 부여해주면 되겠지만,

4bit로만 구성하는 경우 위 사진과 같이 i_a[3:0] , i_a[7:4]로 구분해줄 필요가 있다.

- Code

`timescale 1ns / 1ps

module FullAdder_8bit(

input [7:0] i_a,i_b,

input i_Cin, //bitsream시에는 할당 핀 부족으로 0으로 값을 주었다.

output [7:0] o_Sum,

output o_Crry

);

wire w_carry0;

FullAdder_4bit U_FA40(

.i_a(i_a[3:0]),

.i_b(i_b[3:0]),

.i_Cin(i_Cin),

.o_Sum(o_Sum[3:0]),

.o_Crry(w_carry0)

);

FullAdder_4bit U_FA41(

.i_a(i_a[7:4]),

.i_b(i_b[7:4]),

.i_Cin(w_carry0),

.o_Sum(o_Sum[7:4]),

.o_Crry(o_Crry)

);

endmodule- 검증

진리표에 나뉘어진 블럭별로 검증을 해보았다.

가장 우측 스위치부터

A⁰~A³ , B⁰~B³ , A⁴~A⁷,B⁴~B⁷ 로 할당한 상태이고

LED는 우측부터 Sum⁰~Sum⁷이 할당되어 있고, Carry의 출력을 8번째 LED에 할당해 놓았다.

'Study > VerilogHDL' 카테고리의 다른 글

| [Vivado] FSM (Stop Watch, 가산기) with button. (0) | 2023.08.04 |

|---|---|

| 레지스터와 카운터 (0) | 2023.08.04 |

| [Vivado] FSM (Stop Watch, 가산기) (0) | 2023.08.04 |

| [Vivado] 2 bit Counter, 4x1 Mux, Clock Divider (0) | 2023.08.02 |

| [Vivado] 2x4 Decoder , 7-Segment (0) | 2023.08.02 |