Kraklog

[하만] DAY1.NOT(Inverter) 설계 본문

사용프로그램 : Cadence Virtuoso

Design Rule : Gpdk090

1. 이론

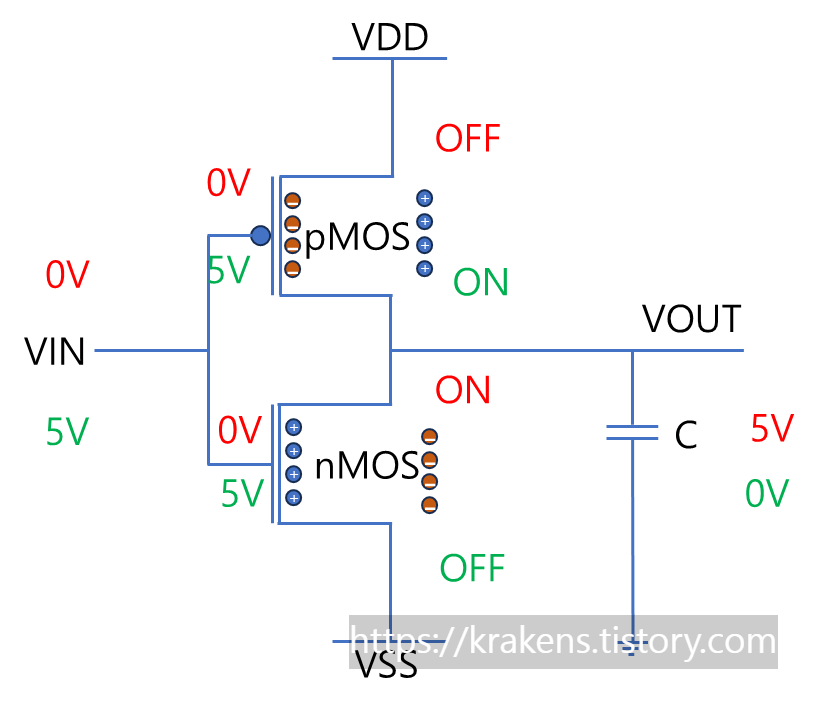

- Schematic Diagram

진리표를 봤을때 입력신호 A가 0에서 1로 변할 때 출력값이 1에서 0으로 변하는 것을 알 수 있다.

즉, 들어오는 입력에 따라 SWITCH 역할을 한다고 생각을 하면 되며, 이런 스위칭 특성을 이용해서 원하는 출력을 설계하는게 주 목표가 되겠다.

따라서 그 목표에 맞춰 인버터는 0V가 입력되면 출력으로 5V, 5V가 입력되면 출력으로 0V가 흐르는 모습을 볼 수 있다.

2. Design

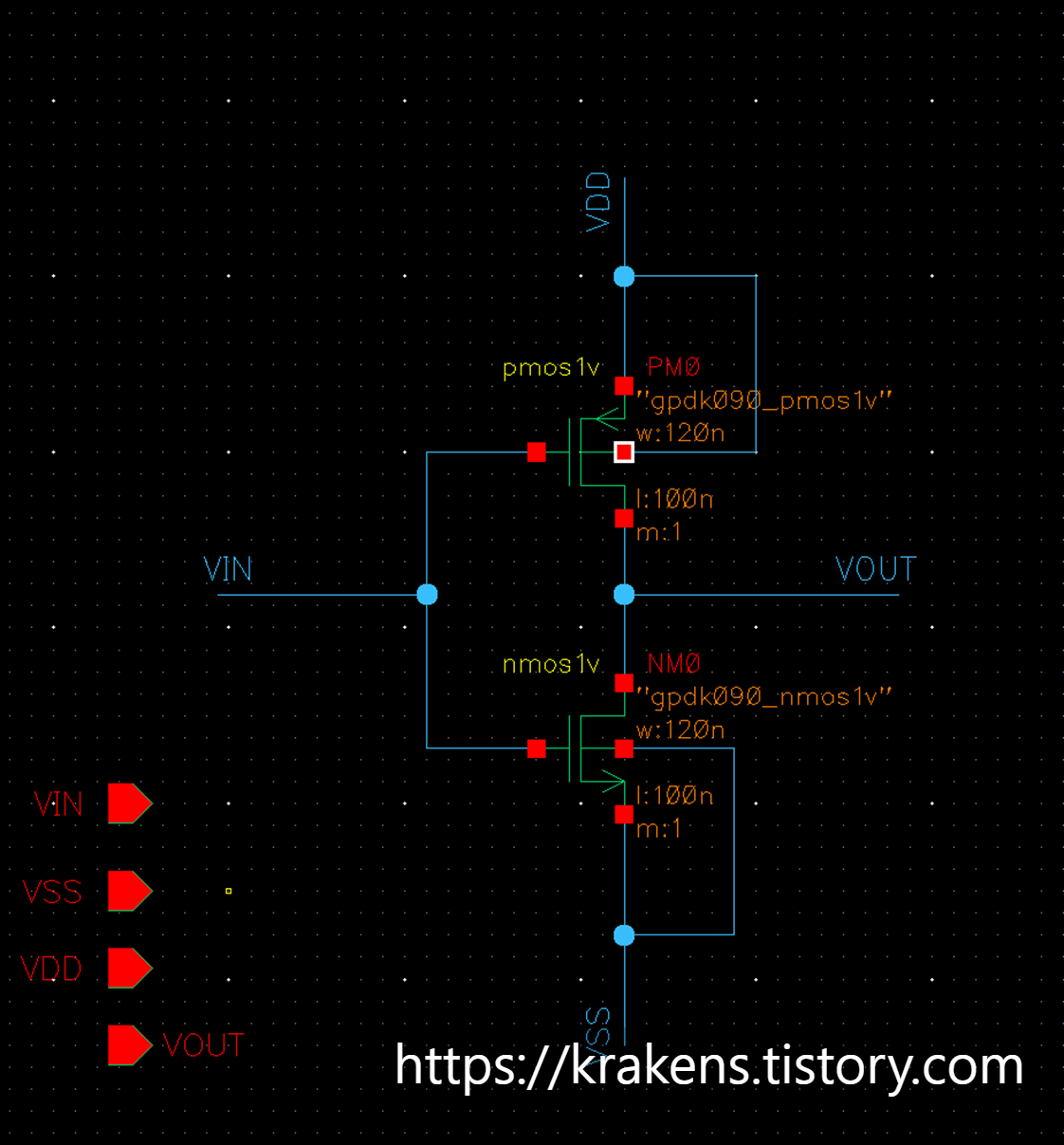

- Schematic 디자인

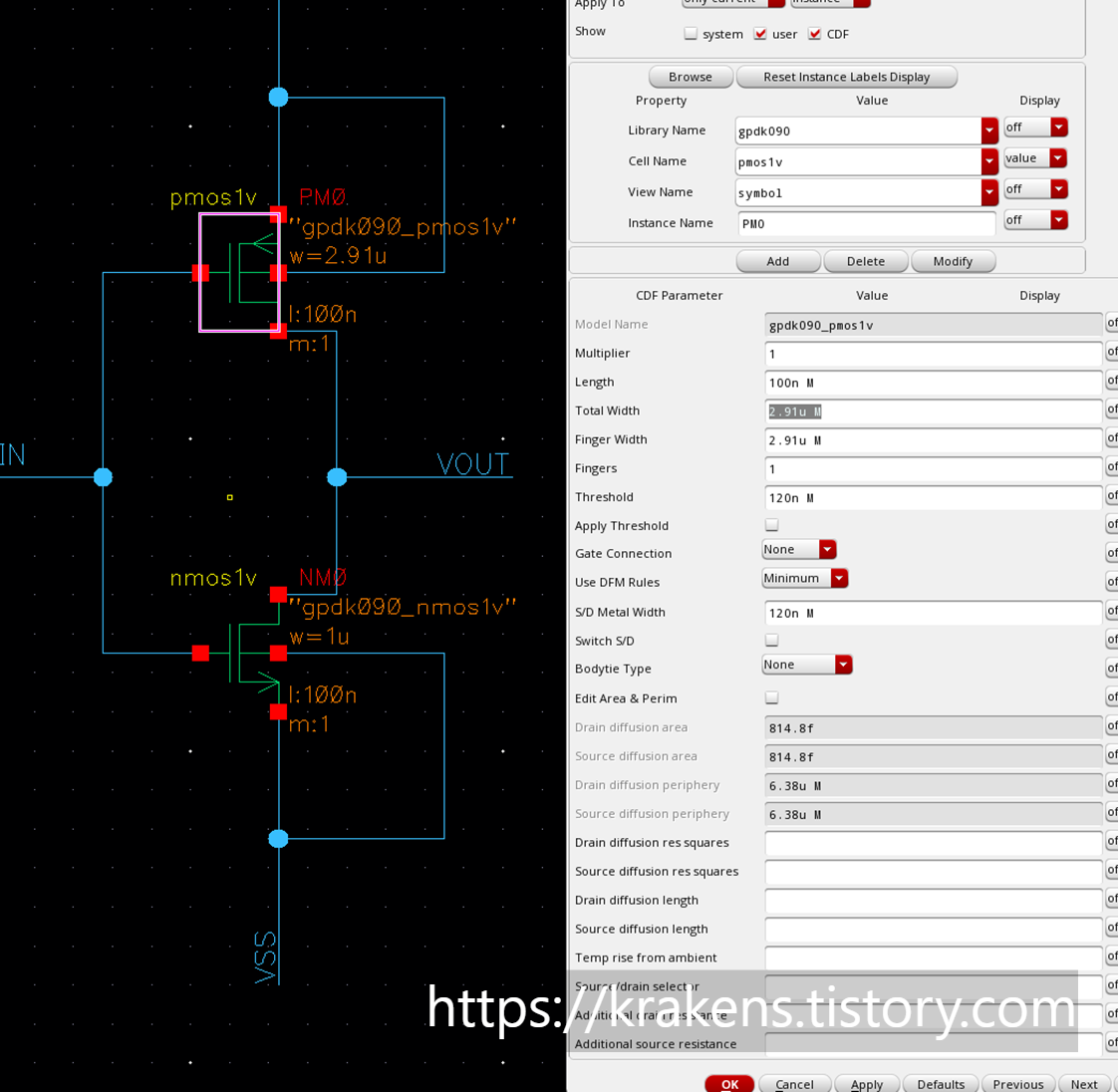

라이브러리에서 New - Cell View 를 통해 Not (혹은 Inverter) 의 Schematic을 생성해준다.

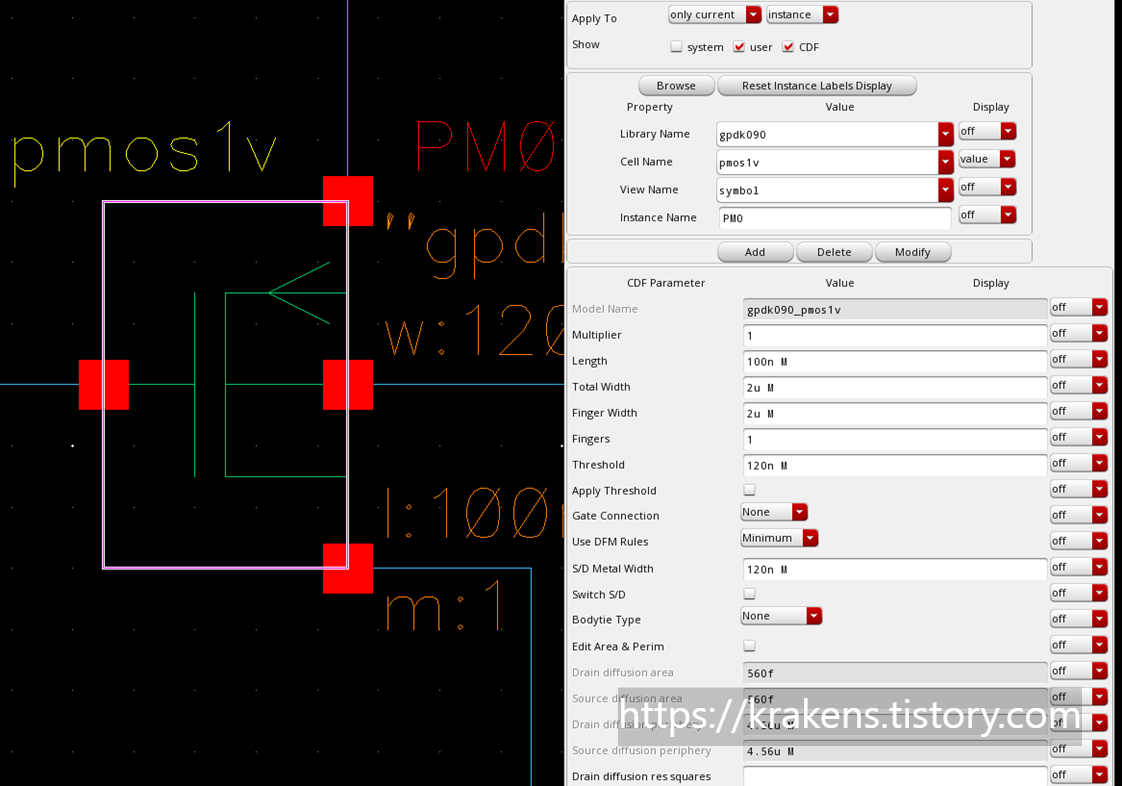

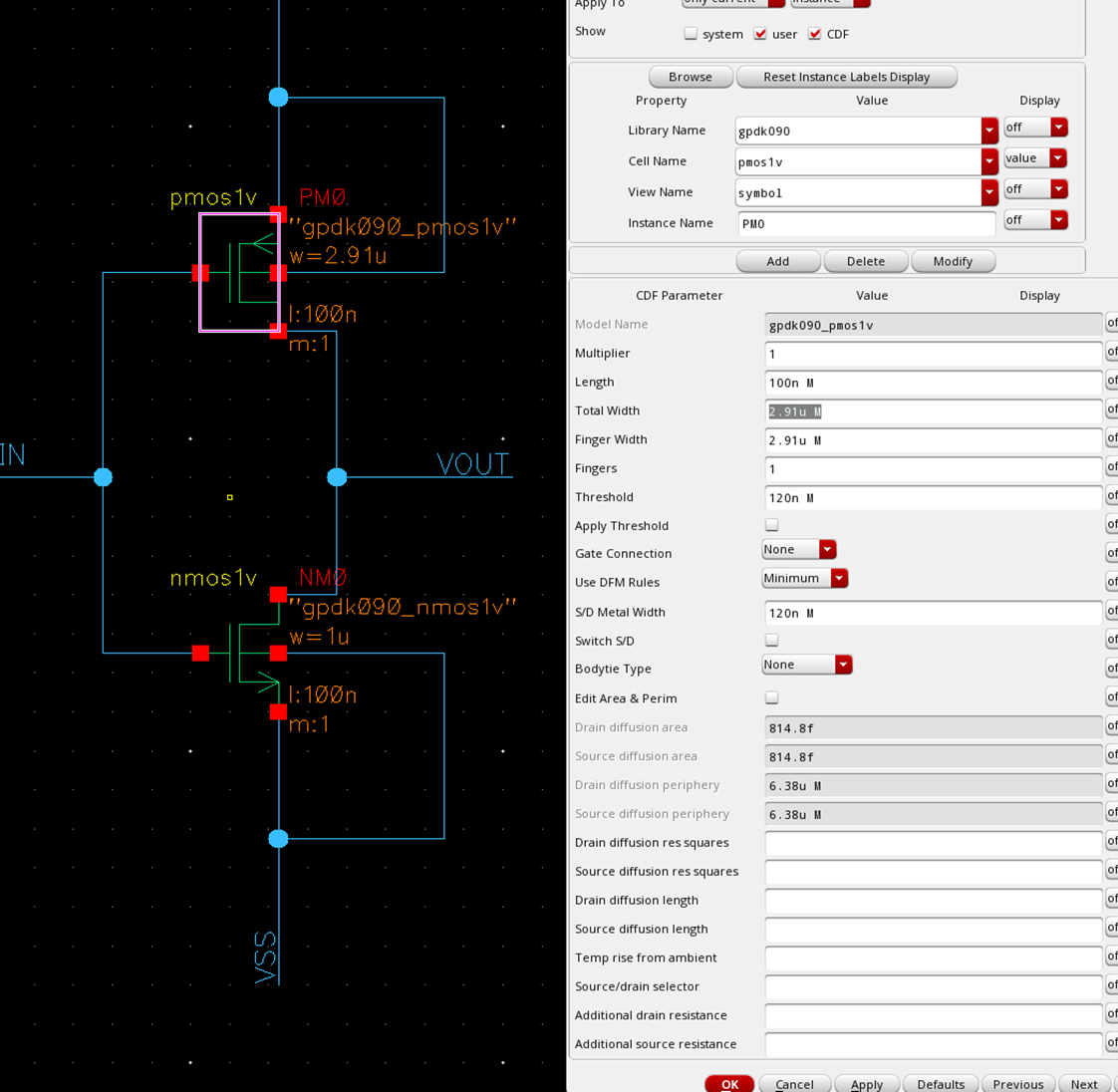

"I"를 눌러 라이브러리에 pMOS와 nMOS심볼을 대입해주고, W를 눌러 설계 목적에 맞춰 배치를 해준다.

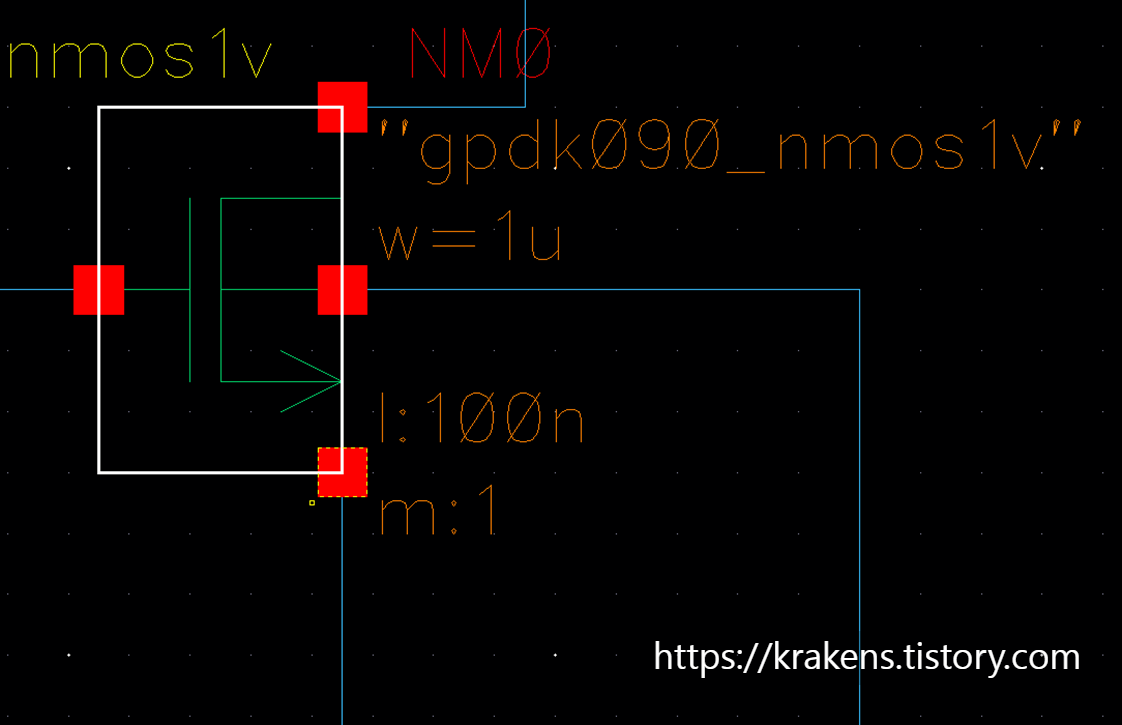

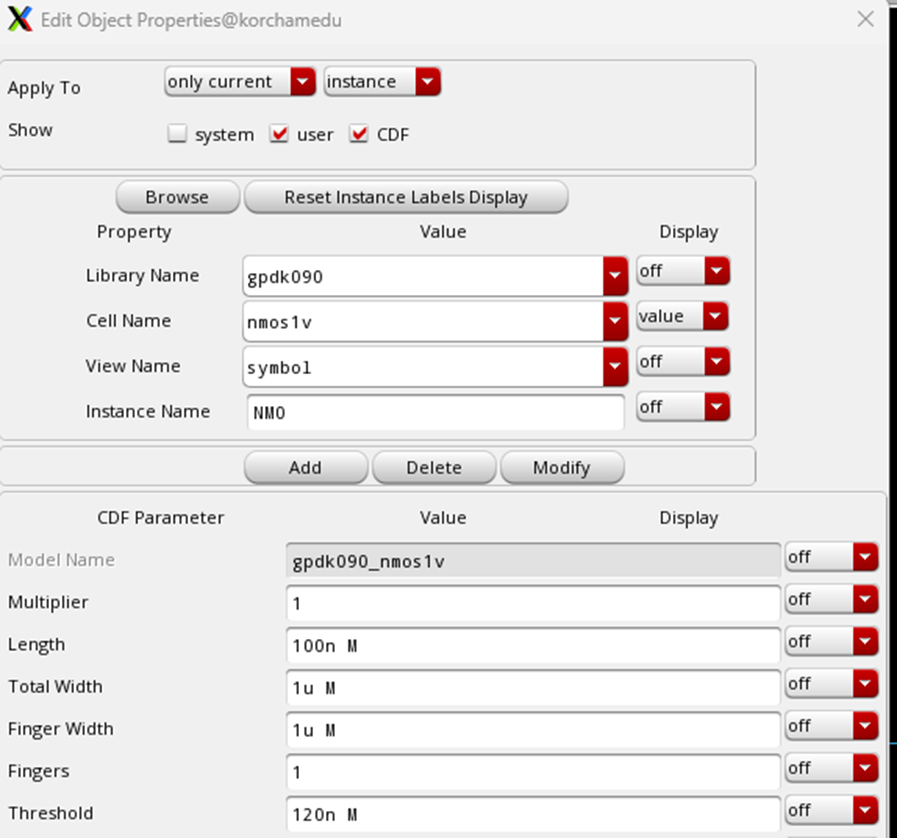

nMOS는 공정의 기본에 맞춰 width를 1u로 변경해주었다.

pMOS의 길이도 설정을 해줘야 하는데 최초에는 대략 2~3배 정도의 차이가 있기에 2u로 설정해주었다.

(그 이유는 밑에 접은글 처리)

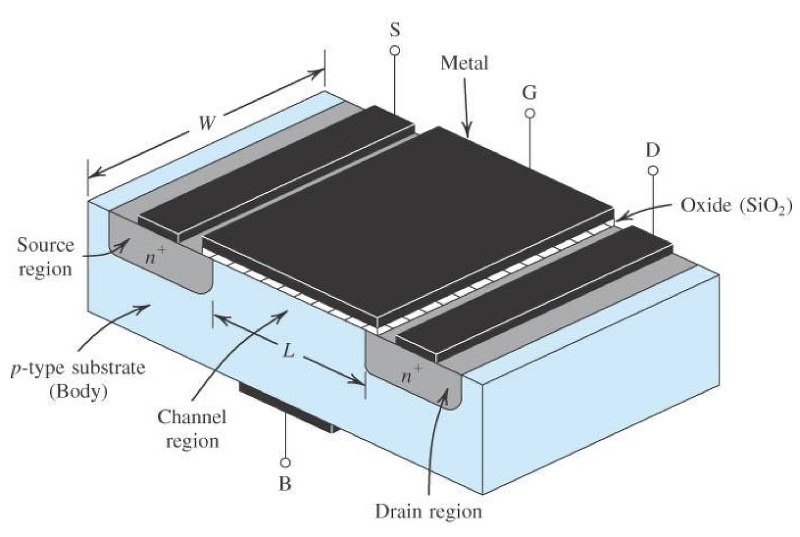

◎ MOSFET

MOSFET

nMOS는 Gate to Source 전압 (VGS) 이 문턱전압(VTH) 보다 작으면 채널이 형성되지 않고, VGS가 VTH보다 클 때 채널이 형성된다. (이상적이라고 가정)

: 채널이 형성 되지 않는다.

: 채널이 형성 된다.

따라서 이를 식으로 표현하면

- Cut Off () :

- Linear ( , ) :

- Saturation (,) :

이때 공정상 설계자가 조절 가능한 값은 W와 L이 되므로 이 값을 통해서 전류값을 조절한다.

- 이때 a는 약 2~3의 값을 갖는다고 본다. (즉, n모스와 p모스는 약 2~3배의 비례관계)ㅇ

3. Simulation

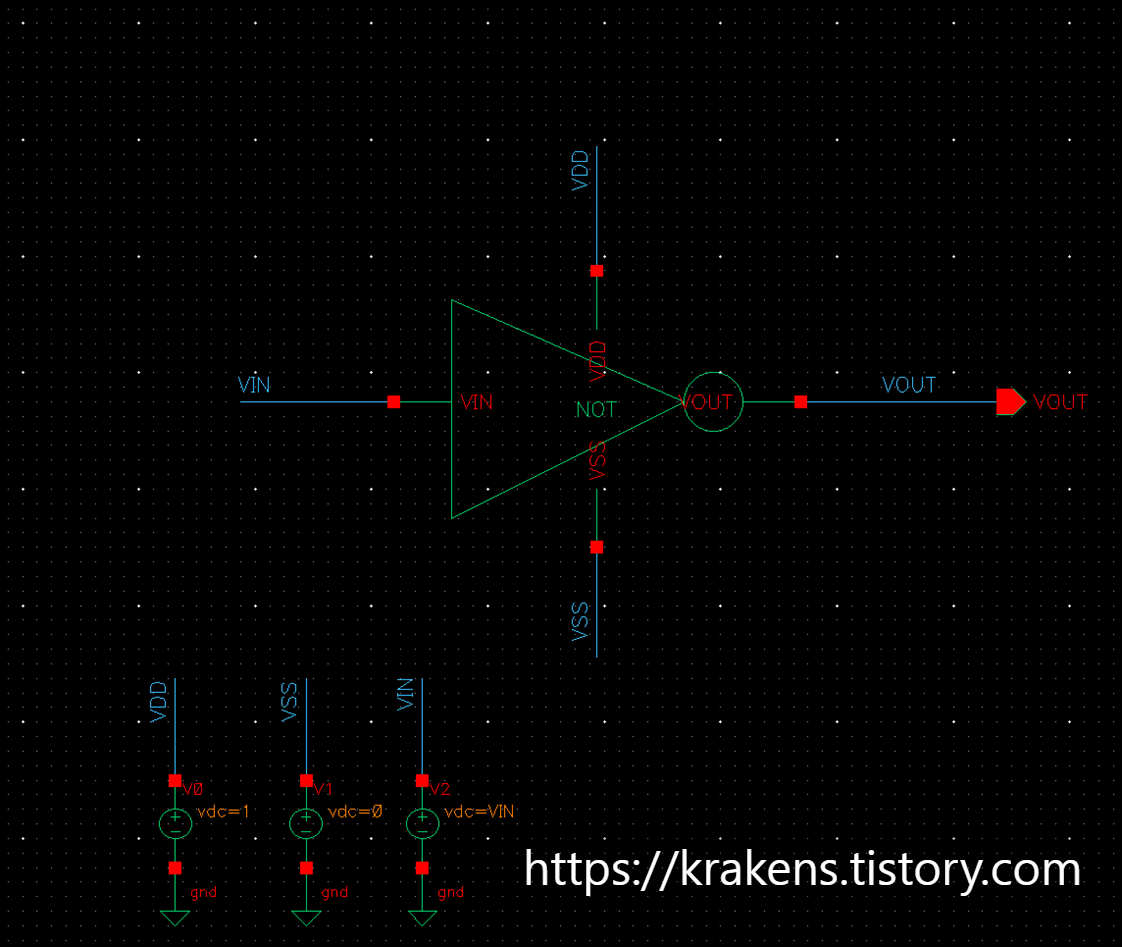

심볼을 작성해주고

pMOS의 적절한 길이를 찾기 위해 시뮬레이션을 해준다.

이때 VDD와 VSS는 1v 0v를 각각 입력했고 (*동작전압) VIN에는 시뮬레이션으로 돌리기 위해 VIN을 설정해주었다.

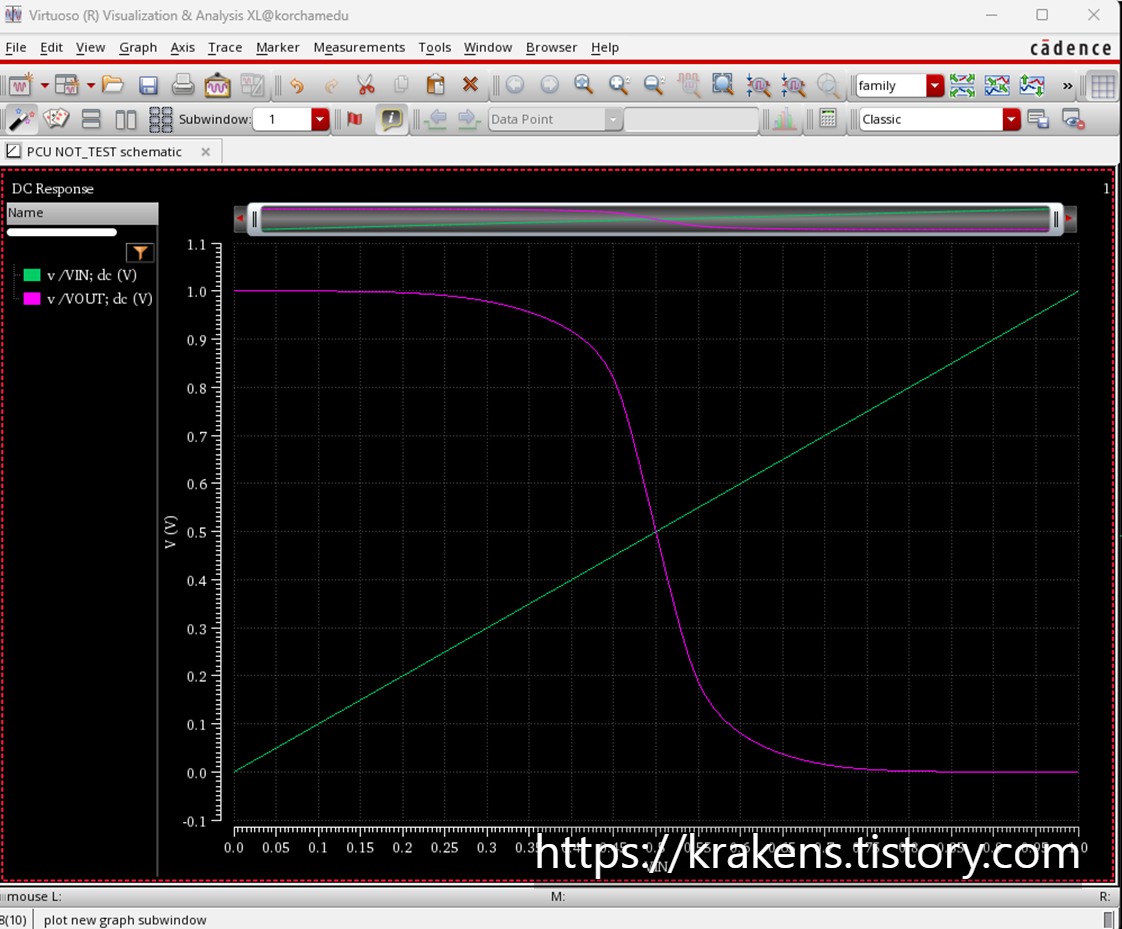

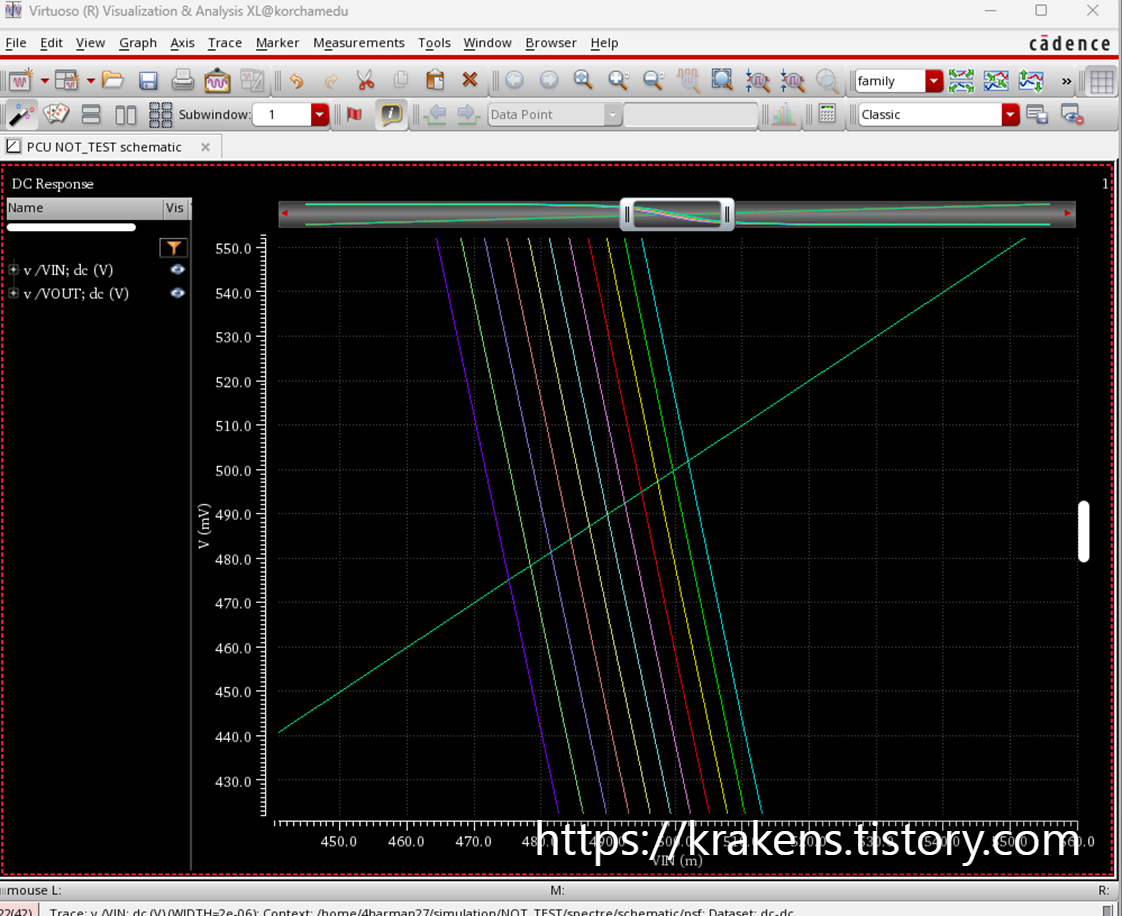

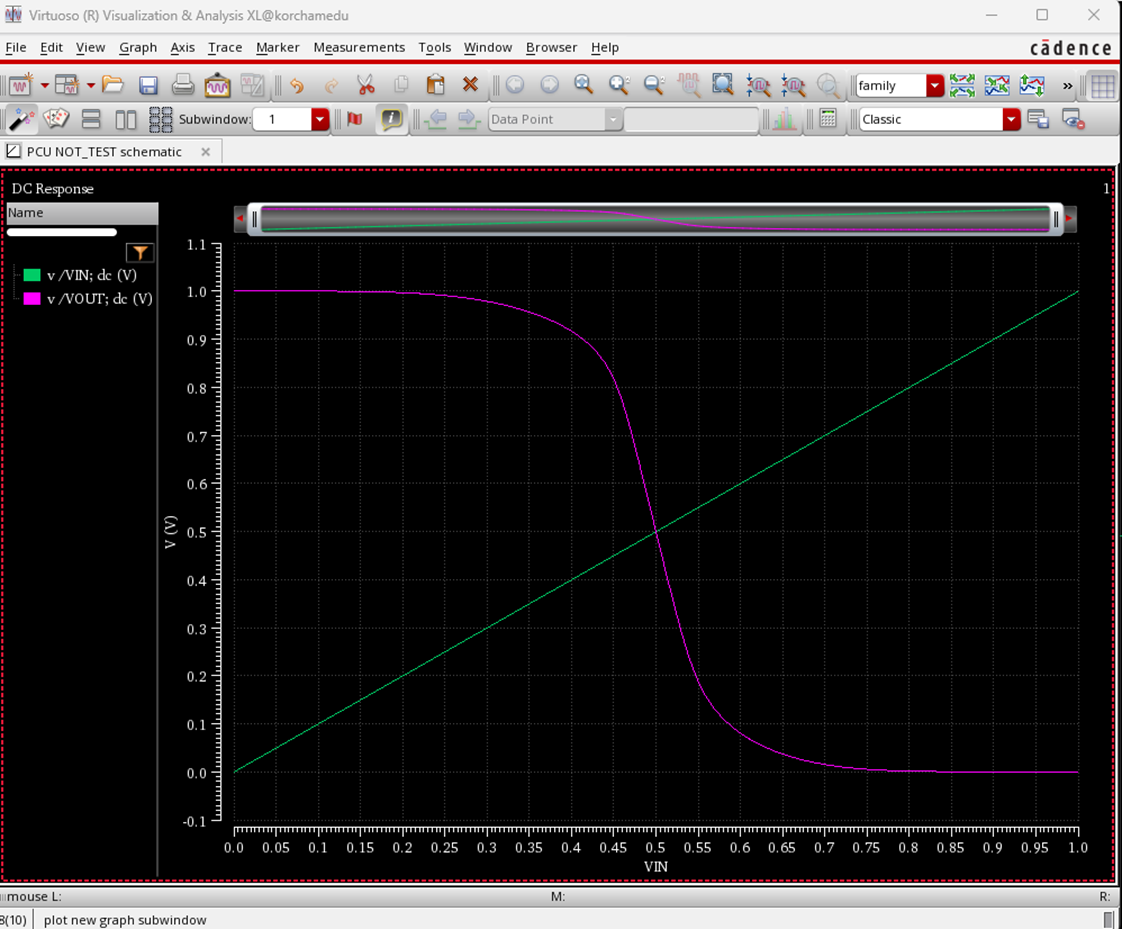

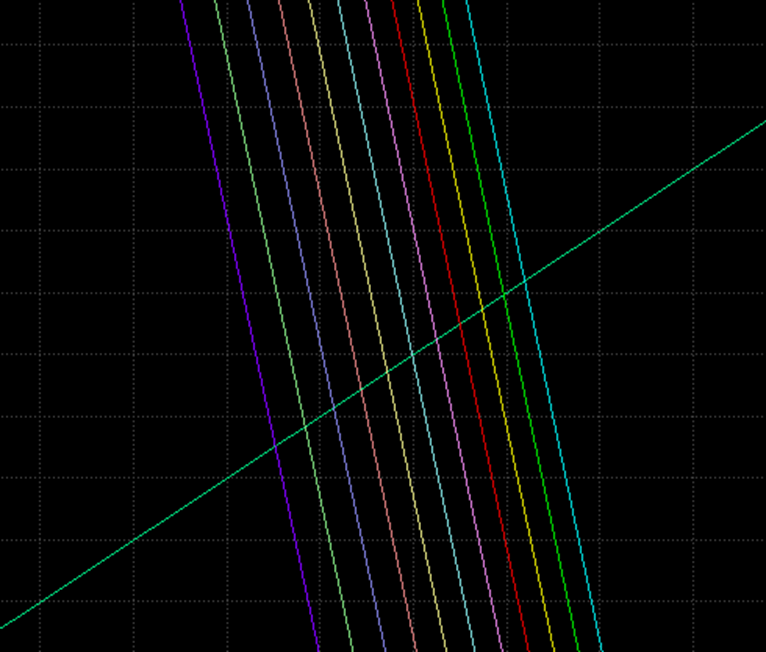

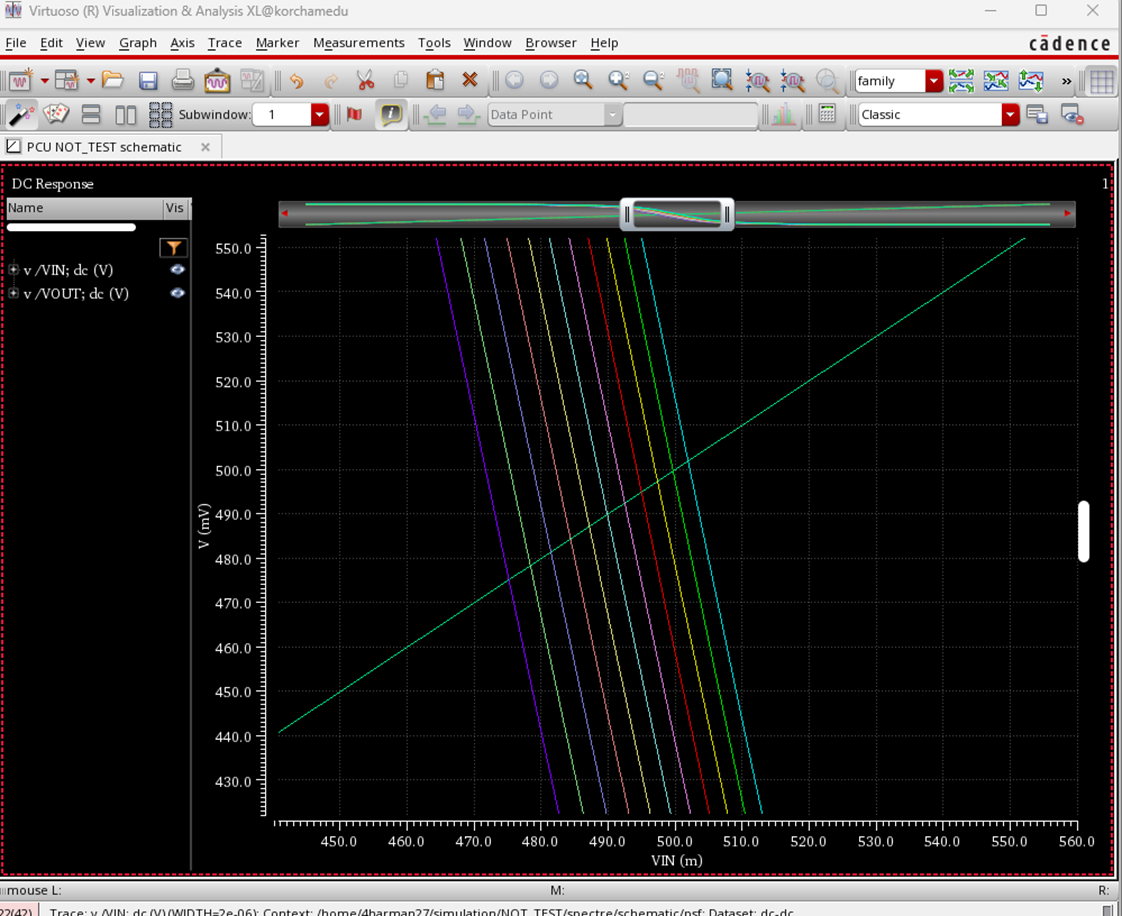

현재 임의로 집어넣은 상태의 그래프, X가 (입력전압) 0.5 부근에서 출력신호(자주색) 가 입력신호(초록색) 와 만나는게 이상적인 동작곡선인데

만일 0.5 기준으로 한 쪽으로 치우쳐 있다면 W의 길이를 조절해서 최대한 근접한 값을 찾아주는게 시뮬레이션의 목적이다.

* 딱 맞추지 못하는 이유 : 예를 들어 소숫점 둘 째자리까지만 공정이 가능하다고 한다면 가장 근사한 값을 찾을 수 밖에 없기 때문.

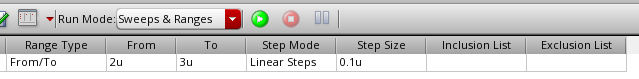

pMOS의 w 정보에 WIDTH를 입력하고 파라미터를 늘려 시뮬레이션을 동작시켰다.

현 과정에서는 3회 정도 시뮬레이션을 통해 적절한 값을 찾을 수 있었다.

1. 시뮬레이션을 통한 값 추론

- Simulation

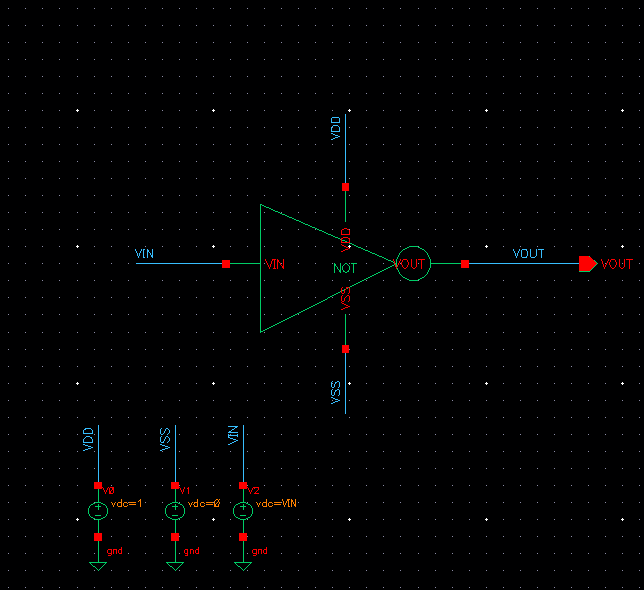

Library Manager 에서 새로운 Cell 을 작성한다.

****_TEST로 명명하고, 시험 환경을 구성해준다.

"I"를 눌러 저번에 작성한 내 라이브러리에서 NOT 심볼을 불러오고,

"I"를 눌러 analogLib 에서 vdc와 gnd 를 불러와 설정해준다.

동작을 위해 VDD와 VSS는 각각 1v와 0v를 넣었고, VIN에는 VIN을 설정해주었다.

(* VIN에 들어가는 값을 시뮬레이션 하기 위해서)

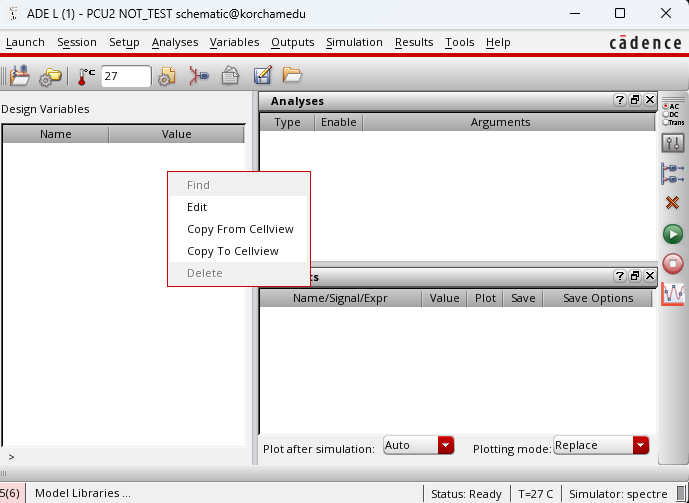

Launch - ADE L 을 눌러 시뮬레이션 툴을 열어준다.

Design Variables에 값을 입력해준다.

그래프의 범위를 0~1v로 잡고 있기 때문에 그 중간값인 0.5v를 측정하기 위해서 500m를 입력하거나 0.5를 입력해준다.

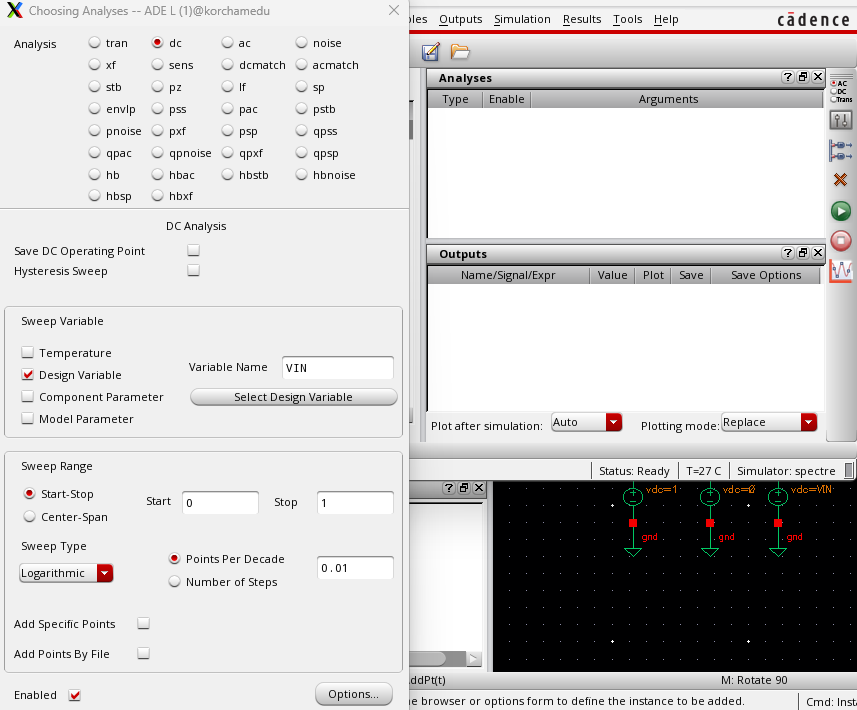

Analyses 에선 분석값을 입력해주어야 하는데, DC전압, 범위설정 등을 해주고 확인을 누른다.

(Sweep Type이 사진상에는 로그로 나왔지만, 선형적으로 볼 것이기 때문에 Linear로 바꿔서 적용했음)

Simulation - Netlist and Run 을 누르고, Results - Direct Plot - main form 을 눌러 결과값을 확인해본다.

여기서는 하나의 값을 설정하고 시뮬을 돌렸기 때문에 입력과 출력의 값에 대한 하나의 그래프만 도시 되었다.

정확한 값을 측정하기 위해, Schematic에서 pMOS의 크기를 WIDTH 로 설정해주고 Cross check and save를 돌렸다.

시뮬레이션 툴에서 Design Variables에서 WIDTH 값을 추가 후 3u를 기입해준다.

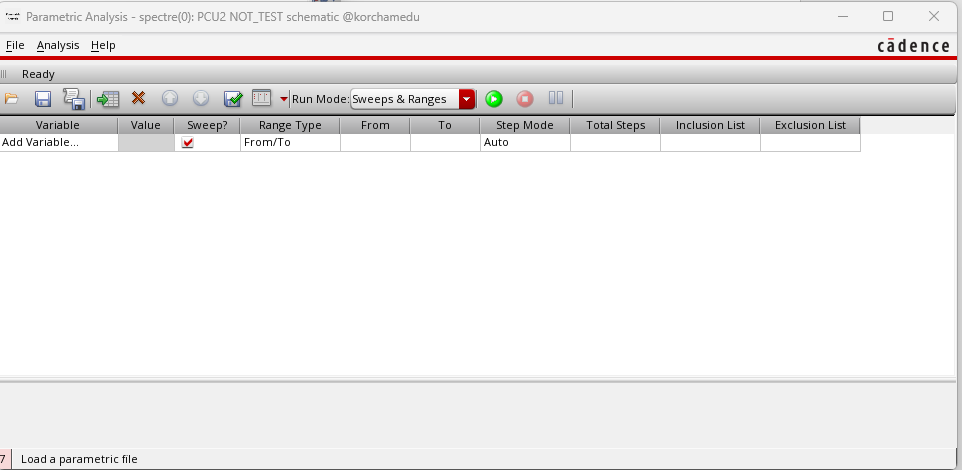

Tools - Parametric Analysis을 열어 Variable에 WIDTH를 설정해주고, 2u ~3u 에 0.1u씩 값을 얻을 수 있도록 설정해주고 시뮬레이션 값을 도시해준다.

0.01u Step Size까지 도출하여 최대한 가까운 값을 찾아서 pMOS의 크기를 조절해주면 Layout을 제외한 도면 작성이 완료된다.

'[Harman] 하만 반도체 설계 > Full Custom One Chip' 카테고리의 다른 글

| [하만] DAY3. LAYOUT 디자인 (0) | 2023.07.08 |

|---|---|

| [하만] DAY2.디지털 논리게이트 설계 (NAND, NOR 작성) (0) | 2023.07.06 |

| [하만] Cadence Virtuoso 초기 사용법 (0) | 2023.07.06 |

| [하만] DAY1.5 - 반도체 이론 용어 (0) | 2023.07.06 |

| [하만] DAY1-CMOS VLSI DESIGN #1 (0) | 2023.07.05 |