Kraklog

[하만] DAY3. LAYOUT 디자인 본문

728x90

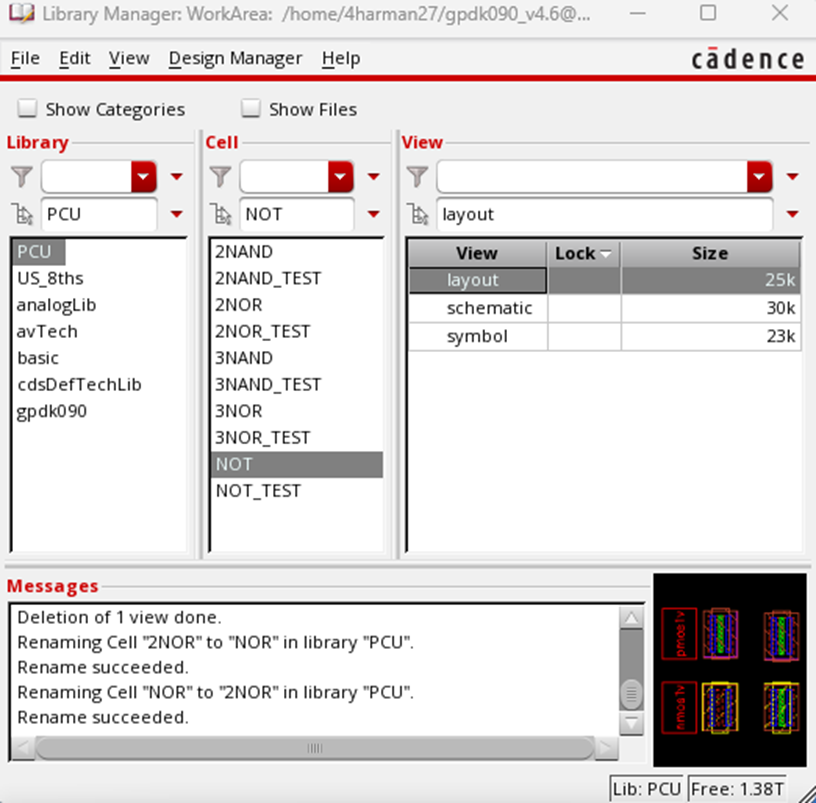

사용프로그램 : Cadence Virtuoso

Design Rule : Gpdk090

1. LAYOUT 구성

- Layout

File - Cellview를 통해 Not 게이트 (인버터) LAYOUT을 생성해줍니다.

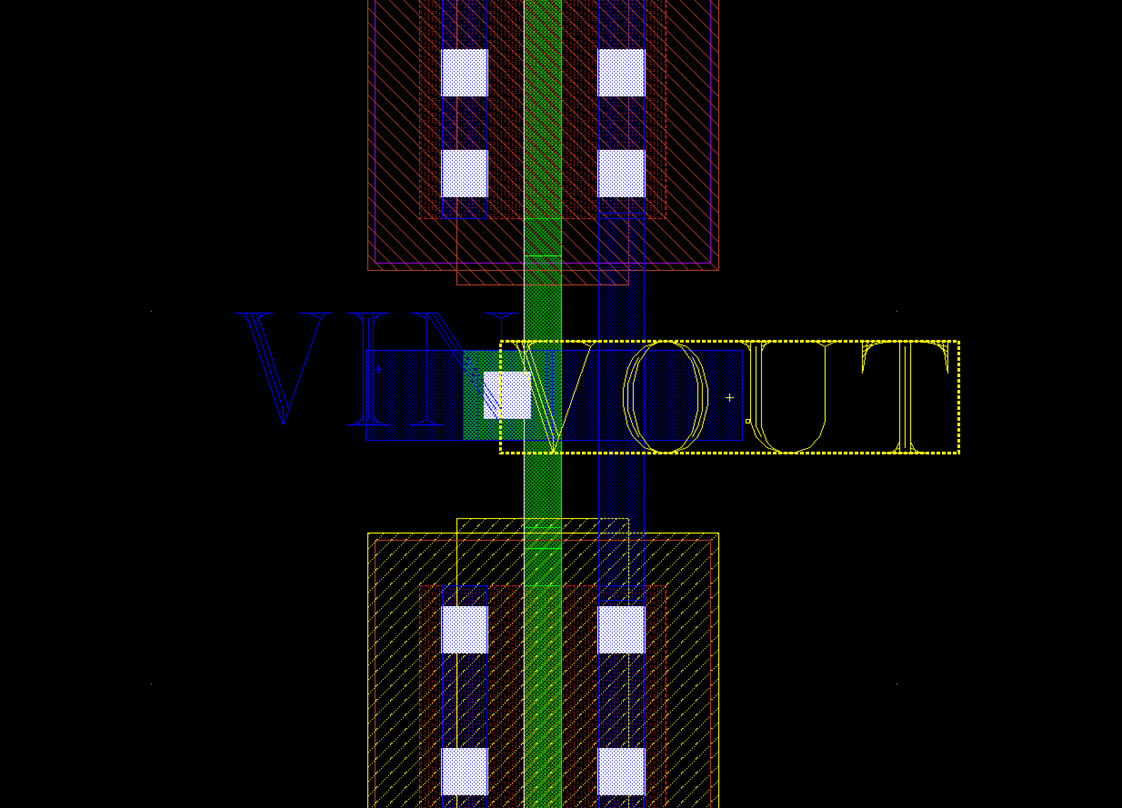

위쪽은 pMOS 아래쪽은 nMOS를 배치해 둡니다. (Schematic 참조 : https://url.kr/u1j8h6)

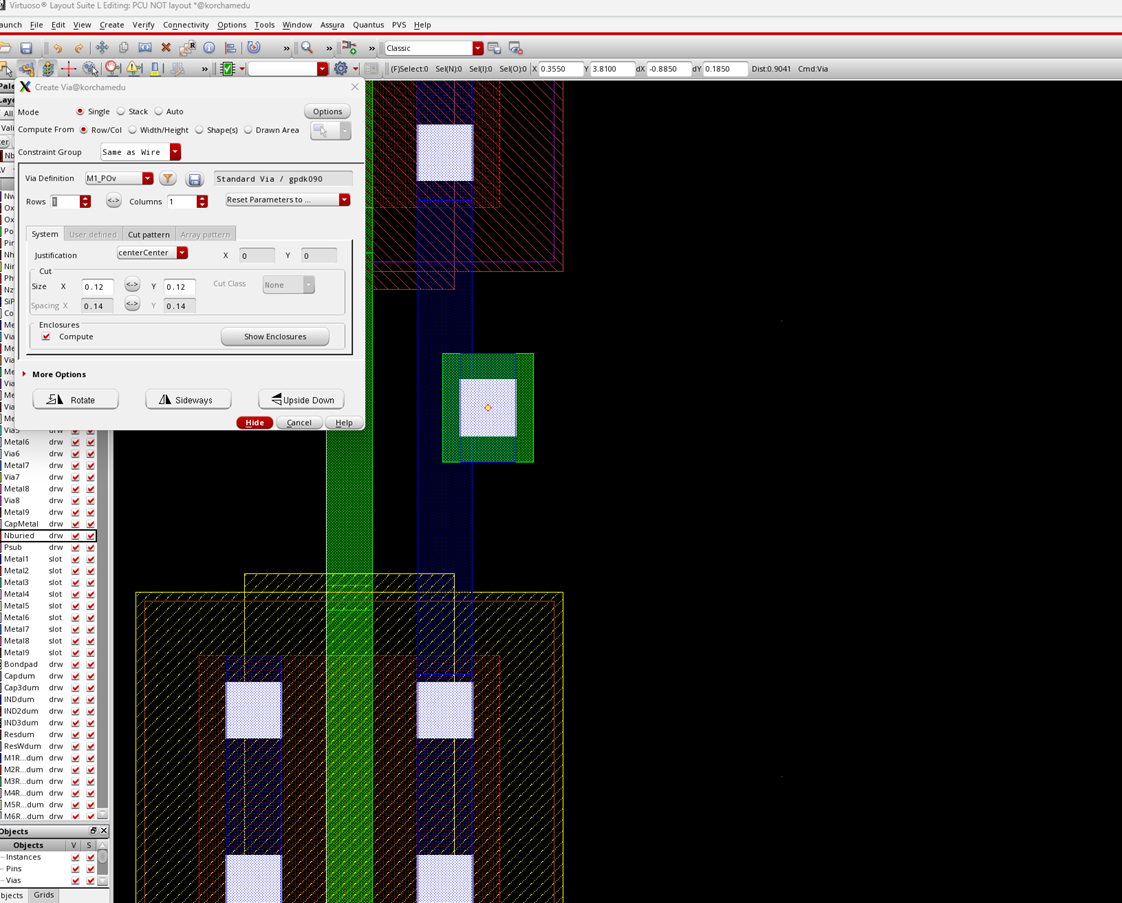

pMOS와 nMOS의 그룹을 풀어 종류를 보면, Poly , Pimp (nMOS : Nimp) , Cont , Oxide 와 Nwell (pMOS)로 구성되어 있으며, 작동을 위해 pSUB, pNwell (전원부)를 규칙에 맞춰 작성해줘야 합니다.

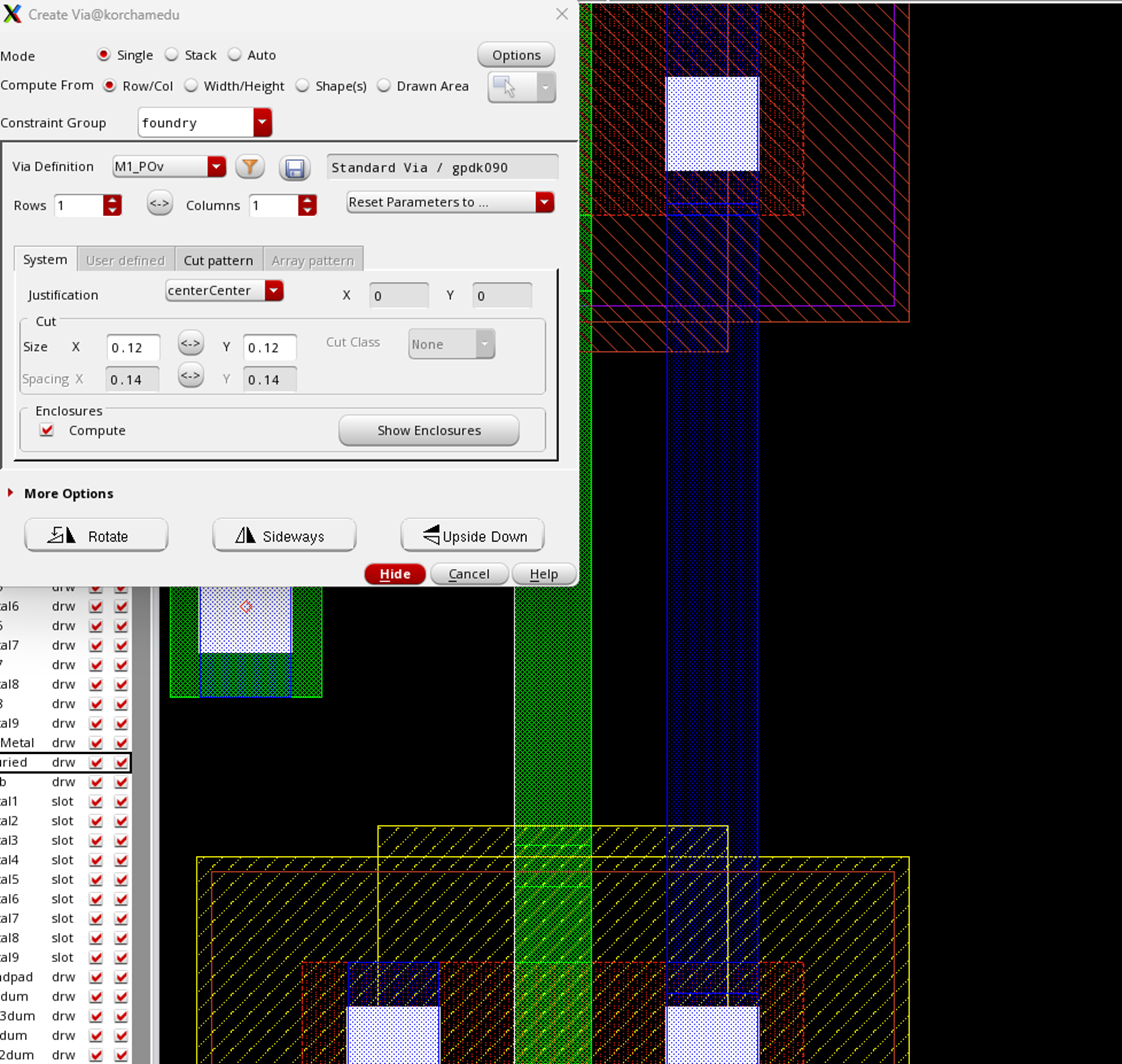

O 키를 눌러 MPov를 작성해줍니다.

이를 Poly에 붙여 신호가 들어오는 VIN을 지정해줍니다.

Schematic에 따르면 pMOS의 VDD는 Source에, 출력핀은 Drain에 연결되어 있기때문에 Metal1을 이용해 그려줍니다.

(R키를 누르면 그릴 수 있고, Path를 이용하기위해선 P를 누르면 그릴 수 있다.)

nMOS에는 출력핀이 Drain에, VSS에는 Source 핀이 연결되어 있으므로, Metal1을 연장하여 그려주었습니다.

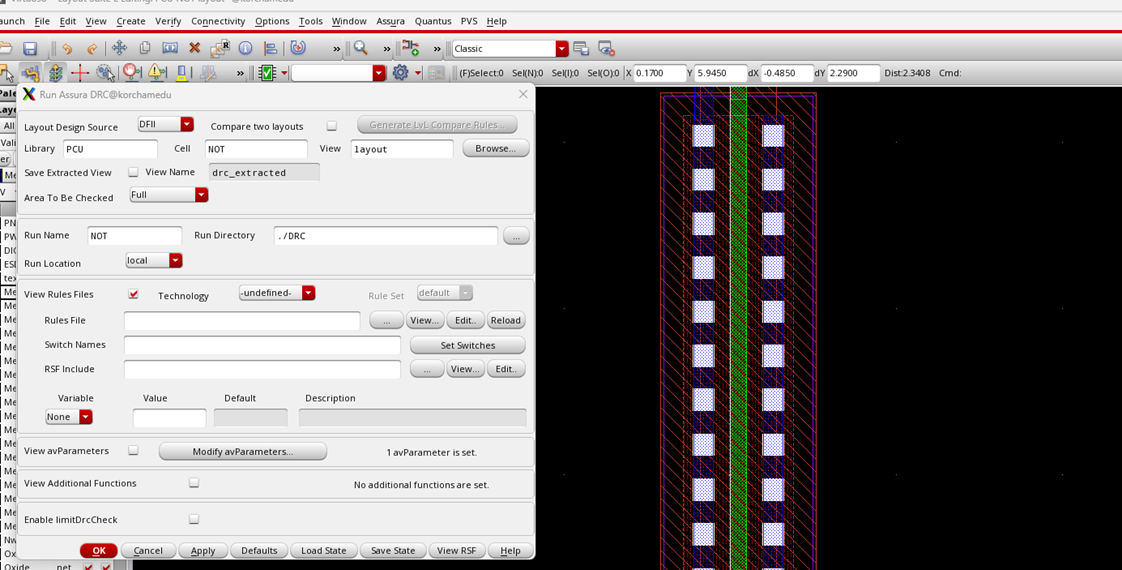

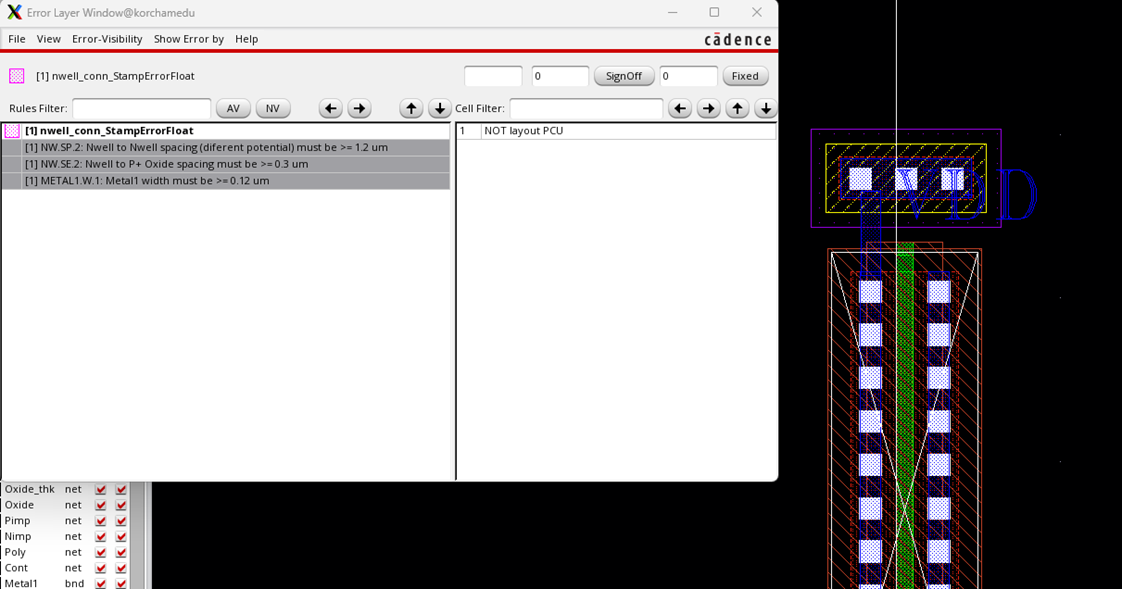

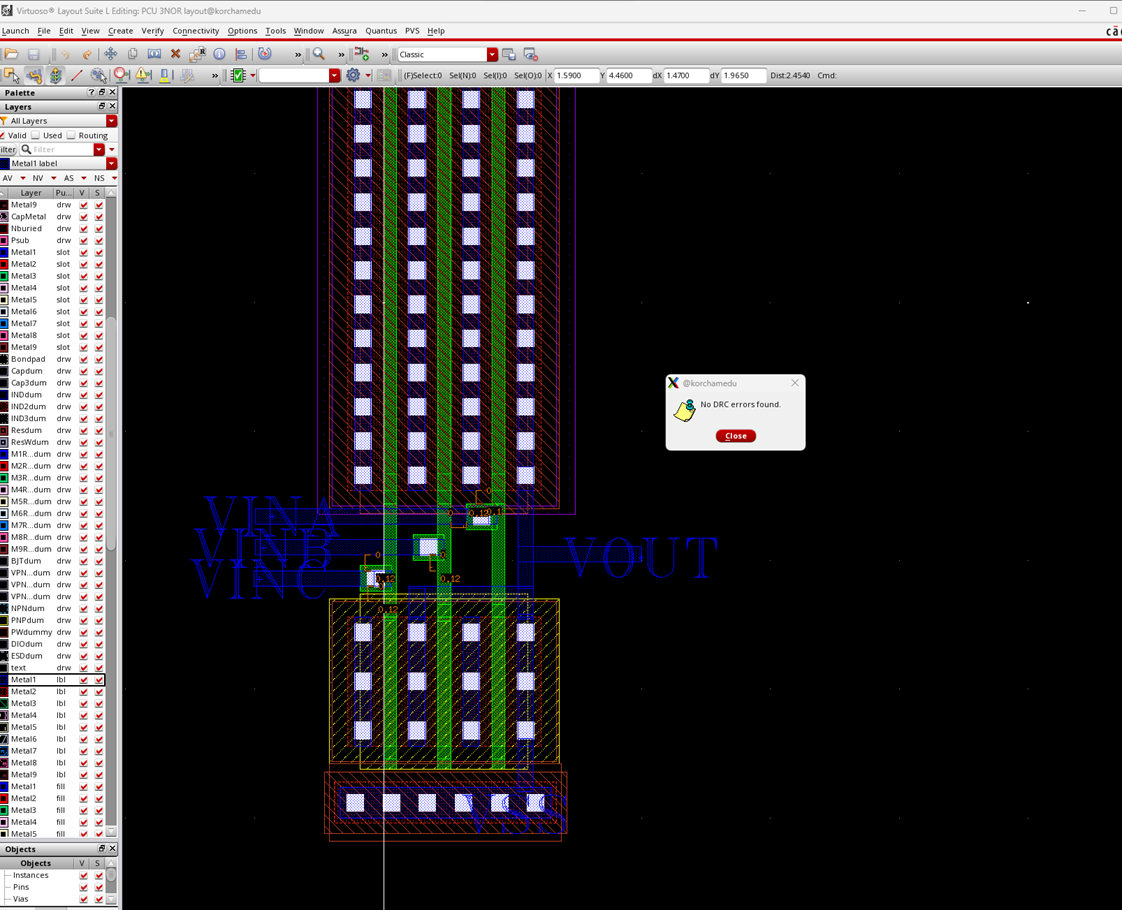

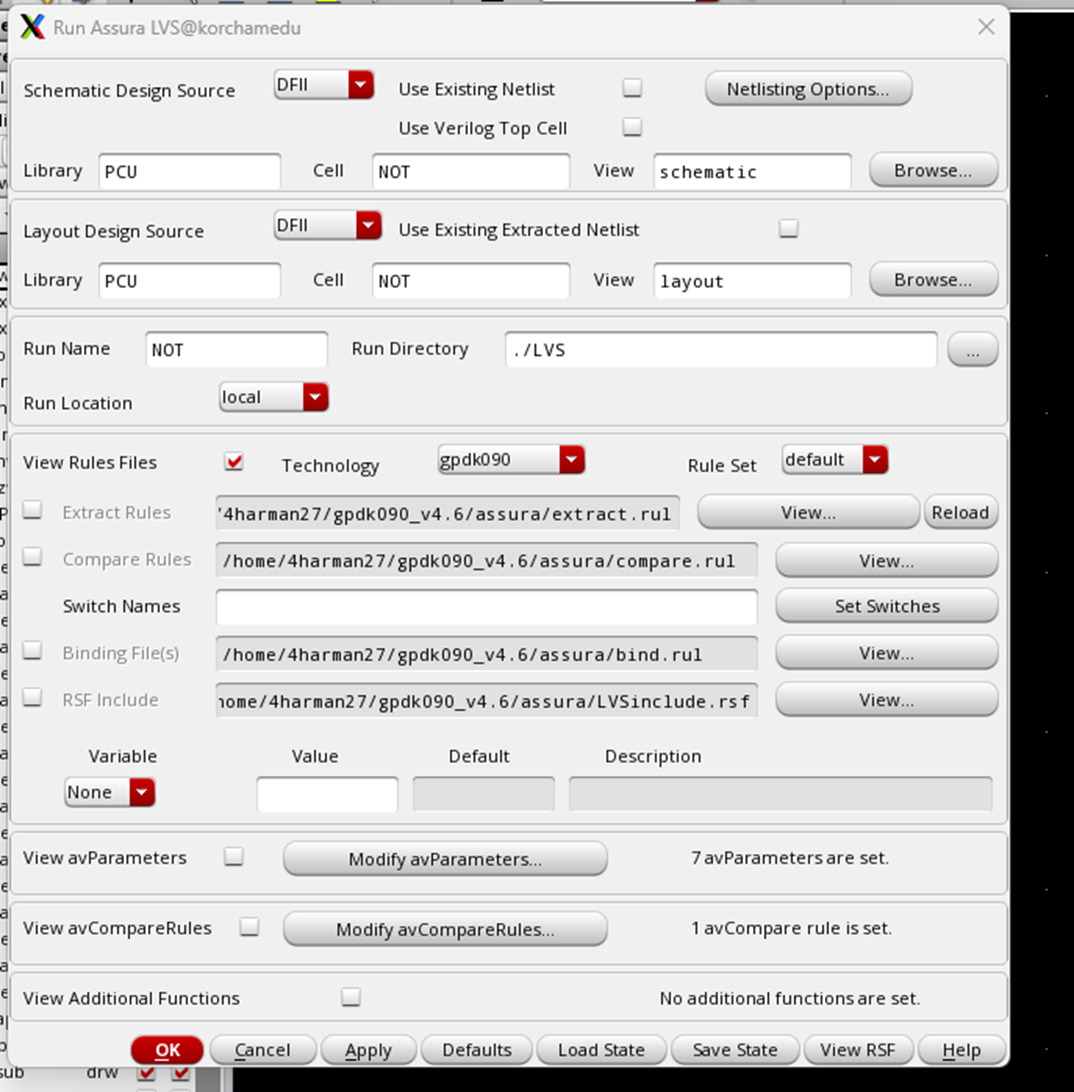

디자인을 끝냈다면, DRC와 LVS 검증 과정을 진행해야합니다

- DRC : Design Rule Check 로 Layout에 설계한 디자인이 규칙에 위배되지 않았는지 검증하는 것

- LVS : Layout versus Schematic , Layout과 Schematic을 비교해서 연결이 정확하게 이루어졌는지 확인하는 작

LVS와 DRC를 충분히 끝냈다면 성공적으로 디자인을 끝낸것입니다.

728x90

'[Harman] 하만 반도체 설계 > Full Custom One Chip' 카테고리의 다른 글

| [하만]DAY5. SWITCH , 21MUX LOGIC & SWITCH 작성 (0) | 2023.07.12 |

|---|---|

| [하만]DAY4. 21MUX LOGIC 작성 (0) | 2023.07.08 |

| [하만] DAY2.디지털 논리게이트 설계 (NAND, NOR 작성) (0) | 2023.07.06 |

| [하만] DAY1.NOT(Inverter) 설계 (0) | 2023.07.06 |

| [하만] Cadence Virtuoso 초기 사용법 (0) | 2023.07.06 |