Kraklog

Day21. 4bit 7-segment, 16bit register, 2bit Counter 본문

[Harman] 하만 반도체 설계/VerilogHDL

Day21. 4bit 7-segment, 16bit register, 2bit Counter

Krakens 2023. 7. 28. 08:28728x90

프로그램 : Quaturs Prime lite edition 18.1

사용문법 : Verilog 2001

보드 : DE1-SOC

Day19. 3bit 7-Segment 이전글 (링크)

module seven_segment_cntrl (

input [3:0] inp ,

output reg seg_a ,

output reg seg_b ,

output reg seg_c ,

output reg seg_d ,

output reg seg_e ,

output reg seg_f ,

output reg seg_g

);

always @(*) begin

case (inp) //if displayed to segment, add '~' in front of 7'000_0000 for invert it.

4'd1 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = ~7'b011_0000; //7'h30;

4'd2 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = ~7'b110_1101; //7'h6D;

4'd3 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = ~7'b111_1001; //7'h79;

4'd4 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = ~7'b011_0011; //7'h33;

4'd5 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = ~7'b101_1011; //7'h5B;

4'd6 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = ~7'b101_1111; //7'h5F;

4'd7 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = ~7'b111_0010; //7'h72;

4'd8 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = ~7'b111_1111; //7'h7F;

4'd9 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = ~7'b111_1011; //7'h7B;

4'd10 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = ~7'b111_0111; //7'h77;

4'd11 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = ~7'b001_1111; //7'h1F;

4'd12 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = ~7'b100_1110; //7'h4E;

4'd13 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = ~7'b011_1101; //7'h3D;

4'd14 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = ~7'b100_1111; //7'h4F;

4'd15 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = ~7'b100_0111; //7'h47;

default: {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = ~7'b111_1110; //7'h7E;

endcase

end

endmodule

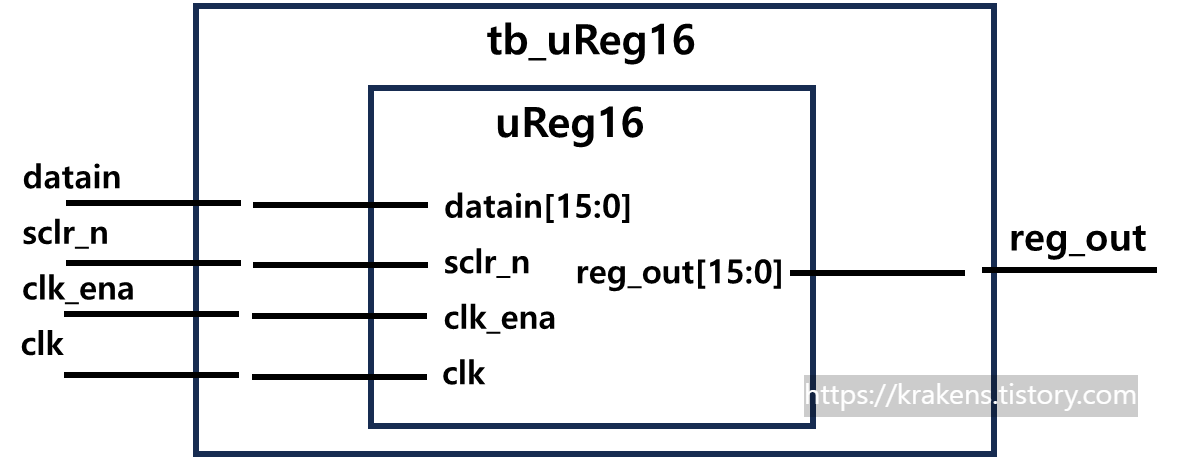

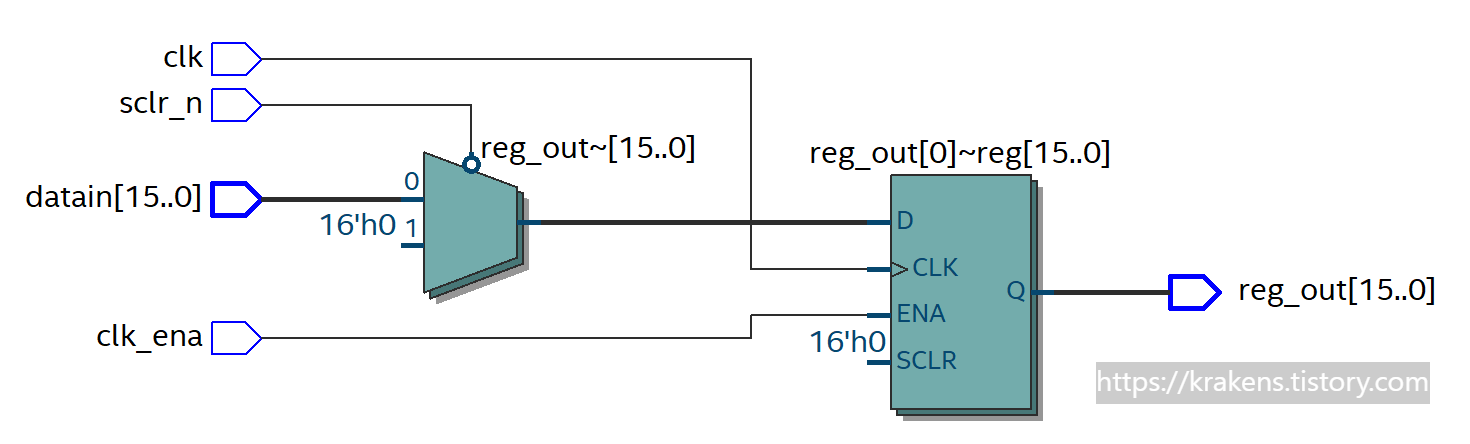

16bit register

module reg16 (

input clk ,

input sclr_n ,

input clk_ena ,

input [15:0] datain ,

output reg [15:0] reg_out

);

always @(posedge clk) begin

if (clk_ena) begin

if(!sclr_n)

reg_out = 16'd0;

else

reg_out = datain;

end

end

endmodule

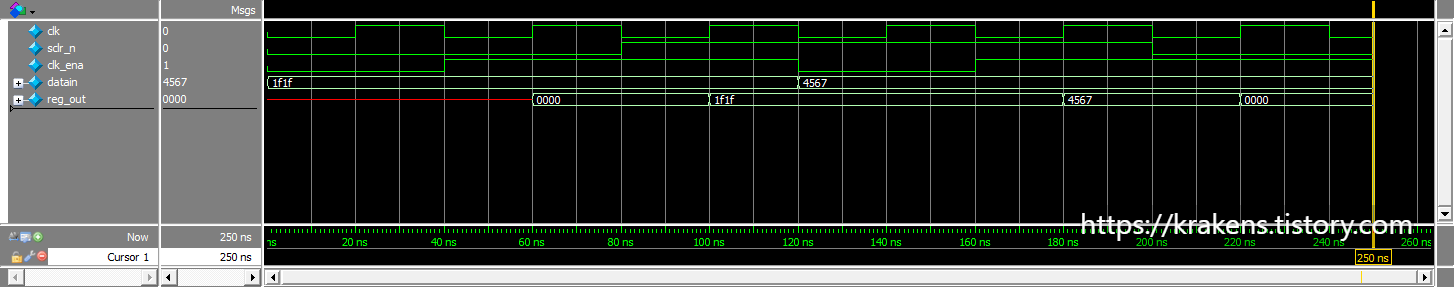

module tb_reg16 ();

reg clk ;

reg sclr_n ;

reg clk_ena ;

reg [15:0] datain ;

wire [15:0] reg_out ;

reg16 uReg16(

.clk (clk ),

.sclr_n (sclr_n ),

.clk_ena (clk_ena),

.datain (datain ),

.reg_out (reg_out)

);

initial begin

clk = 0;

forever

clk = #20 ~clk;

end

initial begin

clk_ena = 1'b0;

sclr_n = 1'b0;

datain = 16'h1F1F;

#40 ; clk_ena = 1'b1;

#40 ; sclr_n = 1'b1;

#40 ; datain = 16'h4567; clk_ena = 1'b0;

#40 ; clk_ena = 1'b1;

#40 ; sclr_n = 1'b0;

end

endmodule

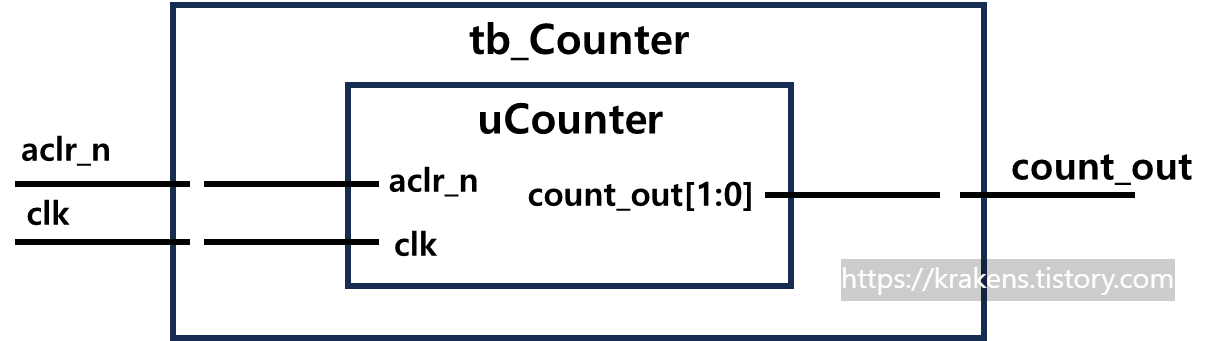

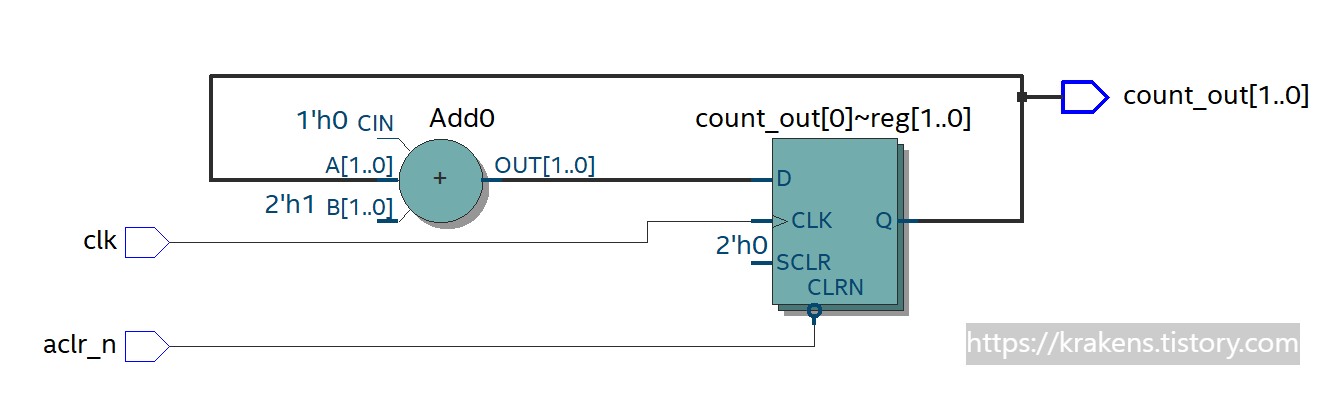

module counter (

input clk ,

input aclr_n ,

output reg [1:0] count_out

);

always @(posedge clk, negedge aclr_n) begin

if(!aclr_n)

count_out = 2'b00;

else

count_out = count_out + 1 ;

end

endmodule

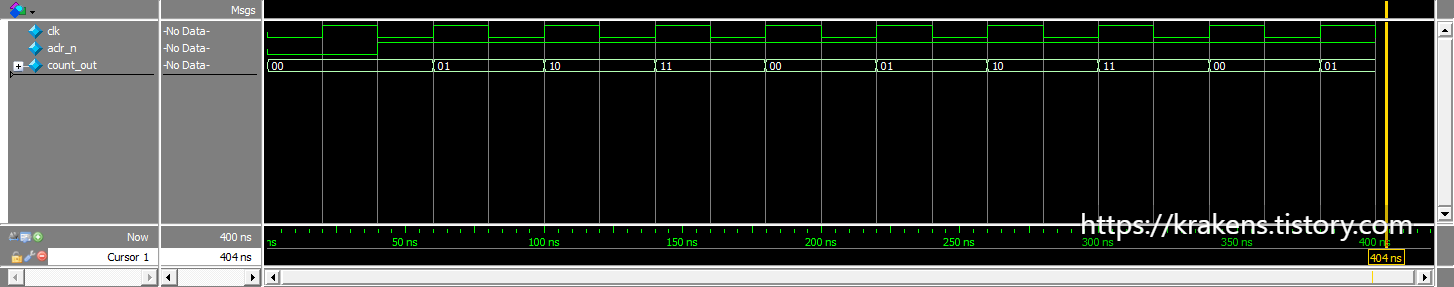

module tb_counter ();

reg clk ;

reg aclr_n ;

wire [1:0] count_out ;

counter uCounter (

.clk (clk ),

.aclr_n (aclr_n ),

.count_out (count_out)

);

initial begin

clk = 0;

forever clk = #20 ~clk;

end

initial begin

aclr_n = 1'b0;

#40 aclr_n = 1'b1;

end

endmodule

728x90

'[Harman] 하만 반도체 설계 > VerilogHDL' 카테고리의 다른 글

| Day23. Simple UART TX,7-seg button&clock (0) | 2023.07.28 |

|---|---|

| Day22. mult control, multiplexer 8x8 (0) | 2023.07.28 |

| Day20. 7-segment (0) | 2023.07.28 |

| Day19. Function Counter (0) | 2023.07.28 |

| Day18. my_rotate (0) | 2023.07.28 |