Kraklog

Day.81 Advanced Verilog #4 본문

728x90

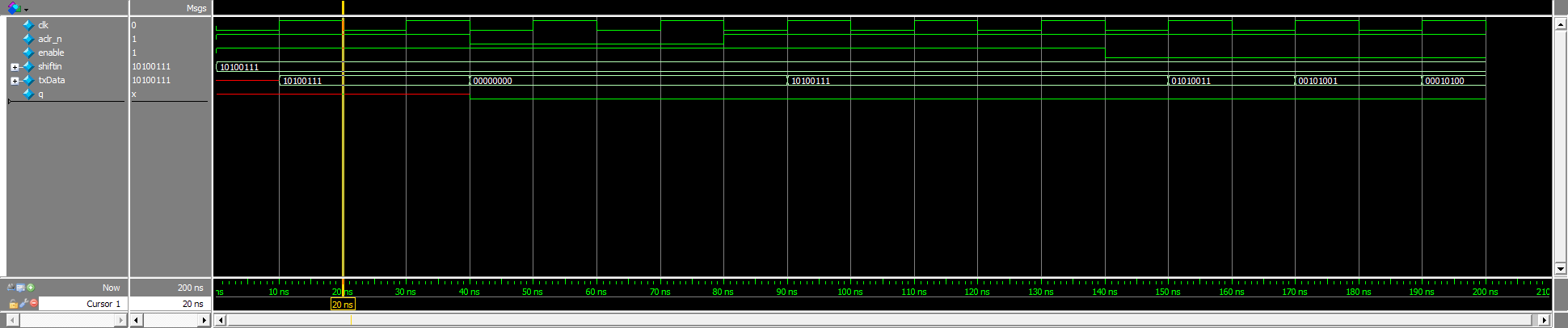

module my_shift_tx (

input clk ,

input aclr_n ,

input enable ,

input [7:0] shiftin , // parallel to serial

output reg q

);

reg [7:0] txData;

wire [7:0] Shiftin_Serial = (enable) ? shiftin : {1'b0, txData[7:1]};

// Parallel to serial shift register

always @(posedge clk or negedge aclr_n) begin

if (!aclr_n)

txData <= 8'b0;

else

txData <= Shiftin_Serial;

end

// Serial out shift register with enable control

always @(posedge clk or negedge aclr_n) begin

if (!aclr_n)

q <= 0;

else if (enable)

q <= q; // Shift q to the right

end

endmodule

`timescale 1ns/1ns

`define CLK_50Mhz 20

module tb_my_shift_tx ();

reg clk ;

reg aclr_n ;

reg enable ;

reg [7:0] shiftin ;

wire q ;

my_shift_tx uMy_shift_tx(

.clk (clk ) ,

.aclr_n (aclr_n ) ,

.enable (enable ) ,

.shiftin(shiftin) ,

.q (q )

);

initial fork

clk_gen();

reset_gen();

ctrl_gen();

data_gen();

join

task clk_gen;

begin

clk = 0;

forever #(`CLK_50Mhz/2) clk = ~clk;

end

endtask

task reset_gen;

begin

aclr_n =1'b1;

repeat(2) @(negedge clk);

aclr_n =1'b0;

repeat(2) @(negedge clk);

aclr_n =1'b1;

end

endtask

task ctrl_gen;

begin

enable = 1'b0;

repeat (6) @(negedge clk);

enable = 1'b1;

@(negedge clk);

enable = 1'b0;

end

endtask

task data_gen;

begin

enable = 1'b1;

shiftin=8'hA7;

end

endtask

endmodule

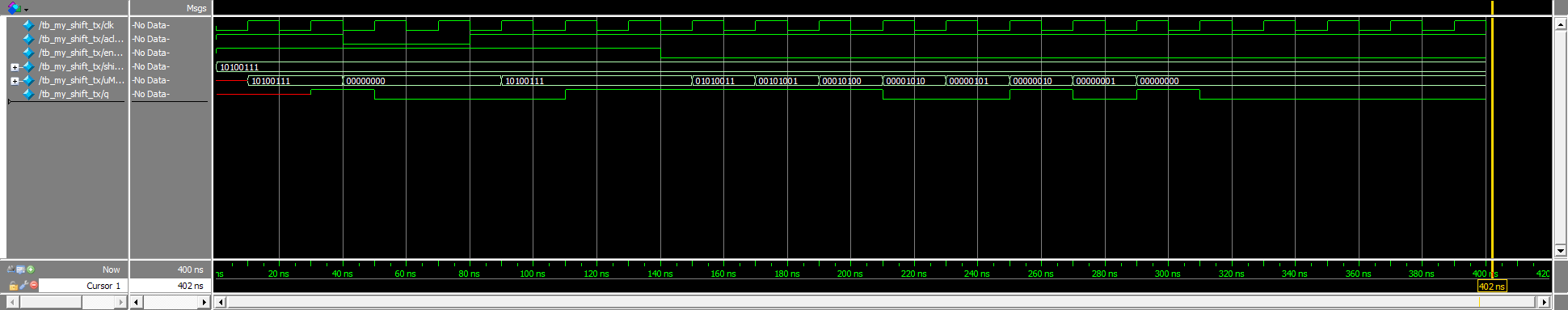

module my_shift_tx (

input clk ,

input aclr_n ,

input enable ,

input [7:0] shiftin , // parallel to serial

output reg q

);

reg [7:0] txData;

wire [7:0] Shiftin_Serial = (enable) ? shiftin : {1'b0, txData[7:1]};

// Parallel to serial shift register

always @(posedge clk or negedge aclr_n) begin

if (!aclr_n)

txData <= 8'b0;

else

txData <= Shiftin_Serial;

end

// Serial out shift register with enable control

always @(posedge clk or negedge aclr_n) begin

if (!aclr_n)

q <= 0;

//else if (enable)

q <= txData[0]; // Shift q to the right

end

endmodule

`timescale 1ns/1ns

`define CLK_50Mhz 20

module tb_my_shift_tx ();

reg clk ;

reg aclr_n ;

reg enable ;

reg [7:0] shiftin ;

wire q ;

my_shift_tx uMy_shift_tx(

.clk (clk ) ,

.aclr_n (aclr_n ) ,

.enable (enable ) ,

.shiftin(shiftin) ,

.q (q )

);

initial fork

clk_gen();

reset_gen();

ctrl_gen();

data_gen();

join

task clk_gen;

begin

clk = 0;

forever #(`CLK_50Mhz/2) clk = ~clk;

end

endtask

task reset_gen;

begin

aclr_n =1'b1;

repeat(2) @(negedge clk);

aclr_n =1'b0;

repeat(2) @(negedge clk);

aclr_n =1'b1;

end

endtask

task ctrl_gen;

begin

enable = 1'b0;

repeat (6) @(negedge clk);

enable = 1'b1;

@(negedge clk);

enable = 1'b0;

end

endtask

task data_gen;

begin

enable = 1'b1;

shiftin=8'hA7;

end

endtask

endmodule

module my_shift_tx (

input clk ,

input aclr_n ,

input enable ,

input [7:0] shiftin , // parallel to serial

output reg q

);

reg [7:0] txData;

wire [7:0] Shiftin_Serial = (enable) ? shiftin : {1'b0, txData[7:1]};

`ifdef DEBUG

// Parallel to serial shift register

always @(posedge clk or negedge aclr_n) begin

if (!aclr_n)

txData <= 8'b0;

else

txData <= Shiftin_Serial;

end

`else

always @(posedge clk, negedge aclr_n) begin

if(!aclr_n)

txData <= 0;

else if

txData <= Shiftin;

else

txData <= {1'b0,txData[7:1]};

end

`endif

// Serial out shift register with enable control

always @(posedge clk or negedge aclr_n) begin

if (!aclr_n)

q <= 0;

//else if (enable)

q <= txData[0]; // Shift q to the right

end

endmodule

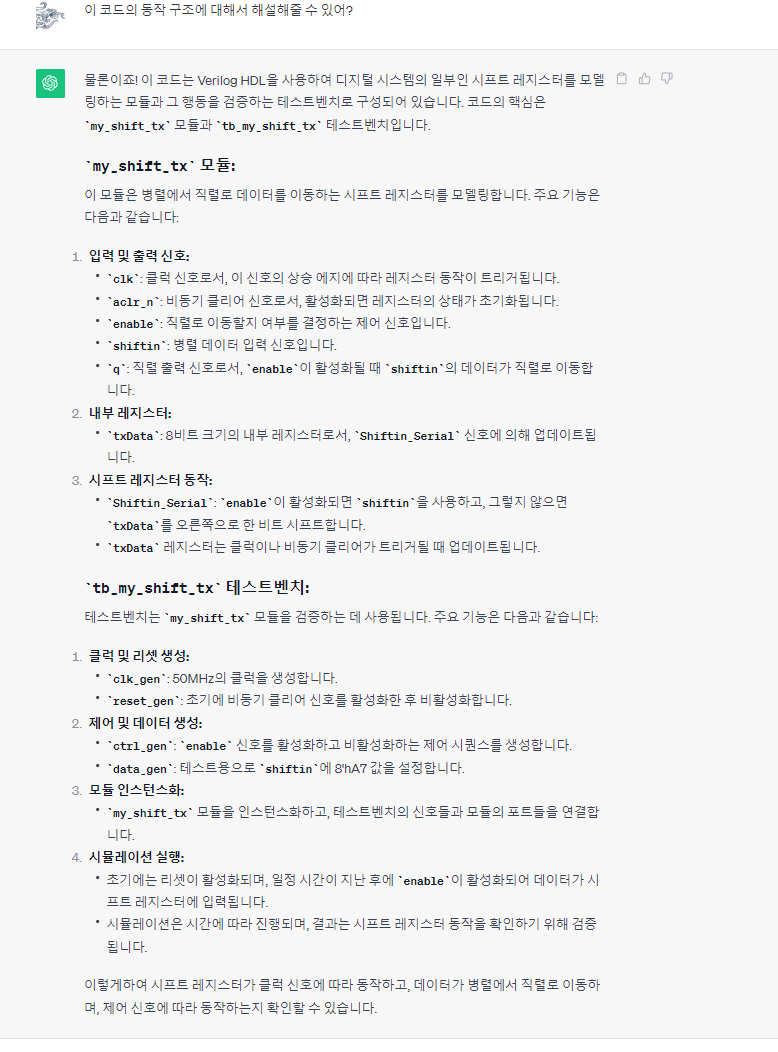

module my_counter(

input clock ,

input aclr_n ,

input clk_ena ,

output reg [7:0] q = 0

);

always @ (posedge clock, negedge aclr_n)

if (!aclr_n)

q[7:0] <= 0;

else if (clk_ena)

q <= q+1;

endmodule

`timescale 1ns/1ns

`define SIZE 8

`define CLK_50Mhz 20

module tb_my_counter ();

reg clock ;

reg aclr_n ;

reg clk_ena ;

wire [`SIZE-1:0] q ;

my_counter uMy_counter (

.clock (clock ) ,

.aclr_n (aclr_n ) ,

.clk_ena(clk_ena) ,

.q (q )

);

initial fork

clock_gen ();

reset_gen();

data_gen();

ctrl_gen();

join

task clock_gen;

begin

clock = 1'b0;

forever #(`CLK_50Mhz/2) clock=~clock;

end

endtask

task reset_gen();

begin

aclr_n = 1'b1;

repeat(2) @(negedge clock)

aclr_n = 1'b0;

repeat(2) @ (negedge clock)

aclr_n = 1'b1;

end

endtask

task data_gen;

begin

end

endtask

task ctrl_gen;

begin

clk_ena = 1'b0;

repeat(20) @(negedge clock)

clk_ena = 1'b1;

repeat(5) @(negedge clock)

clk_ena = 1'b0;

repeat(5) @(negedge clock)

clk_ena = 1'b1;

repeat(5) @(negedge clock)

clk_ena = 1'b0;

end

endtask

endmodule

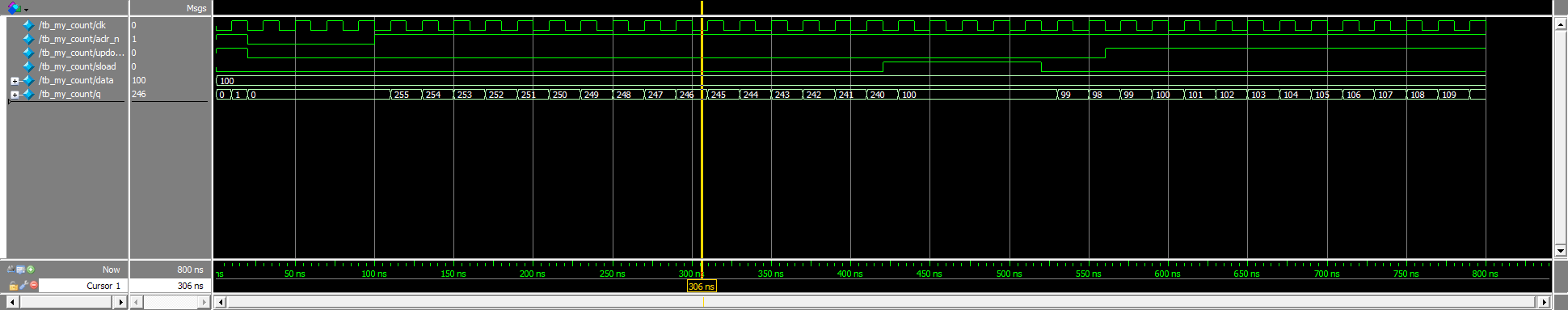

module my_count(

input clk ,

input aclr_n ,

input updown ,

input sload ,

input [7:0] data ,

output reg [7:0] q=0

);

always @(posedge clk, negedge aclr_n)

begin

if (aclr_n == 0)

q[7:0] <= 0;

else if (sload == 1)

q <= data;

else begin

q <= q + (updown ? 1: -1);

end

end

endmodule

`define CLK_50Mhz 20

module tb_my_count();

reg clk ;

reg aclr_n ;

reg updown ;

reg sload ;

reg [7:0] data ;

wire [7:0] q ;

my_count uMy_count(

.clk (clk ) ,

.aclr_n(aclr_n) ,

.updown(updown) ,

.sload (sload ) ,

.data (data ) ,

.q (q )

);

initial fork

clk_gen();

reset_gen();

data_gen();

ctrl_gen();

join

task clk_gen;

begin

clk = 1'b0;

forever #(`CLK_50Mhz/2) clk=~clk;

end

endtask

task reset_gen();

begin

aclr_n = 1'b1;

repeat(4)@(negedge clk)

aclr_n = 1'b0;

repeat(2)@(negedge clk)

aclr_n = 1'b1;

end

endtask

task data_gen;

begin

data=100;

end

endtask

task ctrl_gen;

begin

updown = 1'b1;

sload = 1'b0;

repeat(20) @(negedge clk)

updown = 1'b0;

repeat(5) @(negedge clk)

sload = 1'b1;

repeat(2) @(negedge clk)

sload = 1'b0;

repeat(15) @(negedge clk)

updown = 1'b1;

end

endtask

endmodule

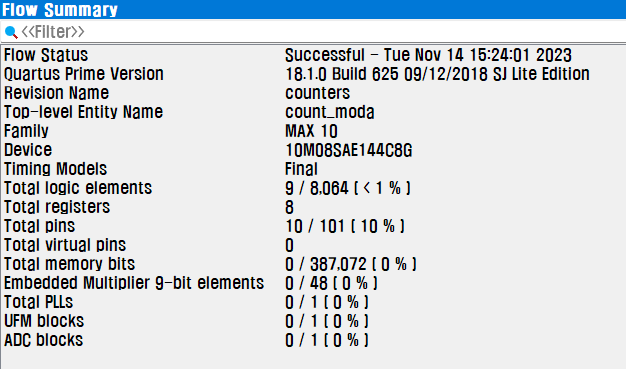

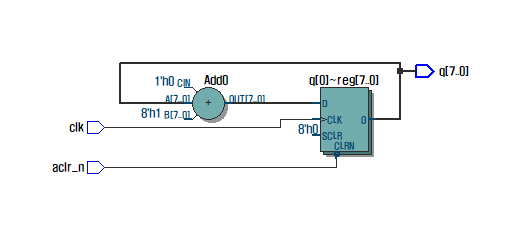

`define MOD_100

module count_moda

`ifdef MOD_100

#(parameter modulus = 100)

`endif

(

input clk ,

input aclr_n ,

`ifdef MOD_100

input updown ,

`endif

output reg [7:0] q=0

);

`ifdef MOD_100

integer direction;

always @(*) begin

if(updown)

direction = 1;

else

direction = -1;

end

`endif

always @(posedge clk, negedge aclr_n)

begin

if (!aclr_n)

q <= 0;

`ifdef MOD_100

else begin

/*if (updown)

direction <= 1;

else

direction <= -1;*/

if ((q ==modulus -1) && (direction ==1))

q<=0;

else if ((q==0) &&(direction == -1))

q <= modulus - 1;

else

q <= q + direction;

end

`else

else

q <= q + 1'b1;

`endif

end

endmodule

`define MOD_100

module count_moda

`ifdef MOD_100

#(parameter modulus = 100)

`endif

(

input clk ,

input aclr_n ,

`ifdef MOD_100

input updown ,

`endif

output reg [7:0] q=0

);

`ifdef MOD_100

integer direction=0;

/*always @(*) begin

if(updown)

direction = 1;

else

direction = -1;

end*/

`endif

always @(posedge clk, negedge aclr_n)

begin

if (!aclr_n)

q <= 0;

`ifdef MOD_100

else begin

if (updown)

direction <= 1;

else

direction <= -1;

if ((q ==modulus -1) && (direction ==1))

q<=0;

else if ((q==0) &&(direction == -1))

q <= modulus - 1;

else

q <= q + direction;

end

`else

else

q <= q + 1'b1;

`endif

end

endmodule윗 코드의 LE가 더 적다.

728x90

'[Harman] 하만 반도체 설계 > VerilogHDL' 카테고리의 다른 글

| Day.83 Advanced Verilog #6 (0) | 2023.11.17 |

|---|---|

| Day.82 Advanced Verilog #5 (0) | 2023.11.15 |

| Day.80 Advavnced Verilog #3 (0) | 2023.11.13 |

| Day.79 Advanced Verilog #2 (0) | 2023.11.10 |

| Day.78 Advanced Verilog #1-원치 않는 Latch 제거 (0) | 2023.11.09 |