Kraklog

Day34. 전자회로 (KCL,KVL,등가회로) 본문

- 키르히호프 법칙

제 1법칙 - 어떤 회로망의 접속 node(점)에 유입되는 전류의 합은 나가는 전류의 합과 같다.

제 2법칙 - 폐회로에서 각 부품에 걸리는 전압의 총합은 0이 된다.

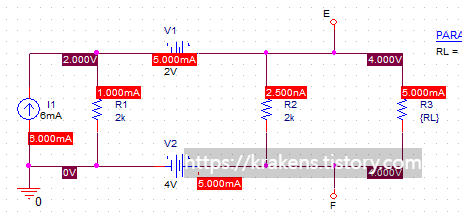

회로해석 : I1은 전류원이기 때문에, 등가내부저항은 ∞Ω이며 전압을 결정할 수 없어 주변 회로에서 결정이 된다.

따라서 R1에 걸리는 전압을 보면 된다.

R1의 걸리는 전압은 1㏀ * 3mA 이므로 3V이다. 따라서 가운데 node를 Va라고 한다면 Va to gnd 는 3V로 계산이 된다.

R2의 걸리는 전류는 Ir2 = (Va-gnd)/r2 = (3-0)/3k = 1mA가 된다. R3, R4도 마찬가지이다.

회로해석 : V1은 전압원이기 때문에 등가내부저항은 0Ω이며, 전류를 결정 할 수 없어 주변회로에서 결정이 된다.

따라서 R1에 걸리는 전류를 계산해서 보면 된다.

Ir1은 다음과 같다. I= (V/R) 이므로 6 / 1k = 6mA이 된다.

윗 회로는 이렇게 바꿀 수 있는데, 단순화하면 그 값은 1kΩ이 된다. 1kΩ에 3mA 전류가 흐르기 때문에 (KCL) 각각 1mA씩 흐르는걸 알 수 있고,

다른 방법으로는

3mA (A에 들어오는 전류 ) = (Va-0)/R2 + (Va-0)/R3 + (Va-0)/R3 = 3Va /3kΩ = Ir2 + Ir3 + Ir4 로 구할 수 있다. 이때 R의 저항 값이 같기 때문에 같은 비율로 전류가 흘러 들어가기 때문에 각 1mA이다.

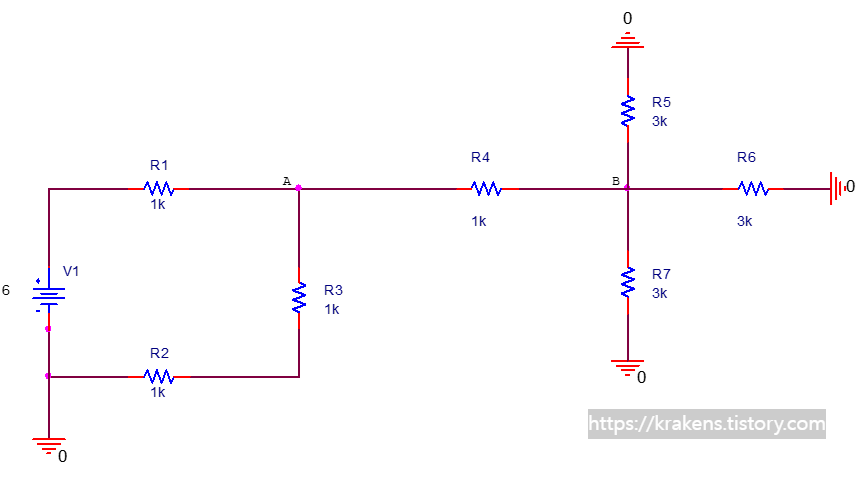

- 회로 계산하기

윗 회로는

A노드를 기준으로 다음과 같이 정리 할 수 있다.

그 결과로 계산하면, Va=3V, Vb=1.5V 임을 알 수 있다.

- 등가회로

테브난 등가회로

노턴 등가회로 - 전력 (Power)

단위시간당 한 일

에너지의 단위 [J], 단위 : [W]

P=VI - 최대 전력 전달 조건

-부하 RL에 최대 전력을 공급하는 조건은 회로의 테브난 등가정항 RTh과 RL이 같을 때임

-신호처리에 RL을 크게, Rs가 가급적 작아야 한다.

-Impedance Matching이 되면 Reflection이 발생하지 않는다.

-Impedance Matching이 깨지면 Reflection 이 발생한다. - 정현파(sinewave)

-주기 : Period, 1cycle의 변화에 필요한 시간 T[sec]

-주파수 : frequency, 1초 동안에 반복되는 cycle 의 수 f[Hz]

-실횻값 : Root Mean Square Value(RMS) 0.707Vm - 과제

'[Harman] 하만 반도체 설계 > 전자회로' 카테고리의 다른 글

| Day40.RLC(공진)#2 (0) | 2023.09.06 |

|---|---|

| Day39.RLC(공진)#1 (0) | 2023.09.06 |

| Day38.인덕턴스 (0) | 2023.09.05 |

| Day 37.커패시턴스 (0) | 2023.09.05 |

| Day33. 회로이론(옴의 법칙) (0) | 2023.08.28 |