Kraklog

DAY9. Full Custom One Chip Design #1 본문

728x90

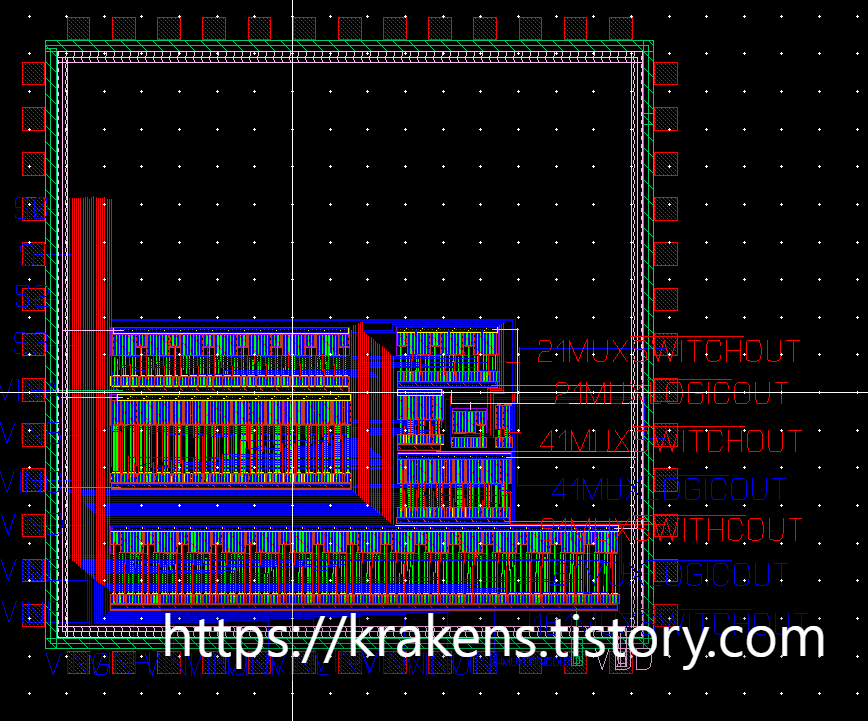

1. 진행상황

- 일반적으로 1,2번 핀이 VSS VDD VDC 핀으로 사용되지만 25 26번 핀으로 옮겨 입력핀과 출력핀 배치

- METAL1 과 METAL2를 가능한 수직으로 배열 (레이어 적층시 신호라인을 겹치지 않게 하기 위해서)

- 161MUX LOGIC을 가장 하단에 배치 ONECHIP에서 가장 길기 때문

- 161MUX SWITCH 을 그 위에 배치, 81MUX LOGIC이 길이가 비슷하기 때문에 윗단에 배치

- 81MUX LOGIC을 세 번째줄에 배치 후 161MUX SWITCH와 입력부를 중앙으로 배치

- 81MUX SWITCH, 41MUX SWITCH (우측 세번째줄), 21MUX SWTICH LOGIC, 가장 위에 41MUX LOGIC 을 배치

- 입력 라인을 전부 중앙으로 배치해 설계 편의 추구 + 입력선의 길이,분기 최소화

- MUX의 경계라인겸, 출력단을 가장 윗부분으로 배치해 최대한 MUX의 출력핀을 단순화

2. 진행예정

- MUX출력핀 선 정리

- Digital Logic Gate 를 하나로 묶어 배치 (크기 최소화)

- 4Bit Adder , 4Bit Adder Subtractor 또한 중앙에 입력선을 가져와 배치

- XOR, Full Adder, Half Adder 를 최대한 하나로 묶어 크기 최소화

- 증폭기 (차동 증폭기, 공통소스 증폭기)는 남은 공간에 맞춰 배치

- 출력핀 배치는 최대한 신경을 쓰겠지만 복잡해질듯 함

728x90

'[Harman] 하만 반도체 설계 > Project' 카테고리의 다른 글

| Day54.전자회로(초음파 거리측정기) (0) | 2023.10.03 |

|---|---|

| Day32. Verilog Project PPT (0) | 2023.08.28 |

| DAY14. ONE CHIP PPT (0) | 2023.07.23 |

| DAY13. Full Custom One Chip Design #2 (0) | 2023.07.21 |

| One Chip 설계 (0) | 2023.07.14 |