Kraklog

Day22. mult control, multiplexer 8x8 본문

728x90

프로그램 : Quaturs Prime lite edition 18.1

사용문법 : Verilog 2001

보드 : DE1-SOC

module mult_control (

input clk ,

input reset_a ,

input start ,

input [1:0] count ,

output reg [1:0] input_sel ,

output reg [1:0] shift_sel ,

output reg [2:0] state_out ,

output reg done ,

output reg clk_ena ,

output reg sclr_n

);

parameter idle=0, lsb=1, mid=2, msb=3, calc_done=4, err=5;

reg [2:0] current_state;

reg [2:0] next_state;

// state register

always @(posedge clk, posedge reset_a) begin

if (reset_a) current_state <= idle;

else current_state <= next_state;

end

// next state combinational logic

always @(*) begin

case (current_state)

idle: begin

if (start) next_state = lsb;

else next_state = idle;

end

lsb: begin

if ((!start)&(count==2'b00)) next_state = mid;

else next_state = err;

end

mid: begin

if ((!start)&(count==2'b01)) next_state = mid;

else if ((!start)&(count==2'b10)) next_state = msb;

else next_state = err;

end

msb: begin

if ((!start)&(count==2'b11)) next_state = calc_done;

else next_state = err;

end

calc_done: begin

if (!start) next_state = idle;

else next_state = err;

end

err: begin

if (start) next_state = idle;

else next_state = err;

end

endcase

end

// (Mealy's FSM) output combinational logic

always @(*) begin

input_sel = 2'bxx;

shift_sel = 2'bxx;

done = 1'b0;

clk_ena = 1'b0;

sclr_n = 1'b1;

case (current_state)

idle: begin

if (start) begin

clk_ena = 1'b1;

sclr_n = 1'b0;

end

end

lsb: begin

if ((!start)&(count==2'b00)) begin

input_sel = 2'b00;

shift_sel = 2'b00;

clk_ena = 1'b1;

end

end

mid: begin

if ((!start)&(count==2'b01)) begin

input_sel = 2'b01;

shift_sel = 2'b01;

clk_ena = 1'b1;

end

else if ((!start)&(count==2'b10)) begin

input_sel = 2'b10;

shift_sel = 2'b01;

clk_ena = 1'b1;

end

end

msb: begin

if ((!start)&(count==2'b11)) begin

input_sel = 2'b11;

shift_sel = 2'b10;

clk_ena = 1'b01;

end

end

calc_done: begin

if (!start) begin

done = 1'b1;

end

end

err: begin

if (start) begin

clk_ena = 1'b1;

sclr_n = 1'b0;

end

end

endcase

end

// (Moore's FSM) output combinational logic

always @(current_state) begin

state_out = 3'b000;

case (current_state)

idle: ;

lsb: state_out = 3'b001;

mid: state_out = 3'b010;

msb: state_out = 3'b011;

calc_done: state_out = 3'b100;

err: state_out = 3'b101;

endcase

end

endmodule`timescale 1 ns/1 ns

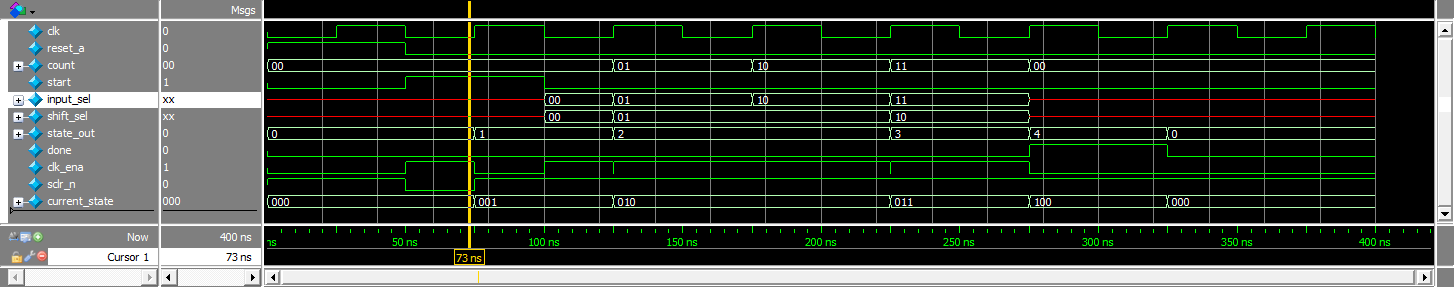

module mult_control_tb();

// Wires to connect to DUT

reg clk, reset_a, start;

reg [1:0] count;

wire [2:0] state_out;

wire [1:0] input_sel, shift_sel;

wire done, clk_ena, sclr_n;

integer i;

// Instantiate unit under test (mult_control)

mult_control mult_control1 (.clk(clk), .reset_a(reset_a), .count(count),

.input_sel(input_sel), .shift_sel(shift_sel), .state_out(state_out),

.done(done), .clk_ena(clk_ena), .sclr_n(sclr_n), .start(start));

// Process to create clock signal

initial begin

clk = 0;

forever clk = #25 ~clk;

end

// Set the reset control

initial begin

reset_a = 1'b1;

#50 reset_a = 1'b0;

end

// Process to control counter

initial begin

count = 2'd0;

#125 ;

for (i=0; i<4; i=i+1) begin

count = count + 1;

#50 ;

end

end

// Start signal control

initial begin

start = 1'b0;

#50 start = 1'b1;

#50 start = 1'b0;

end

endmodule

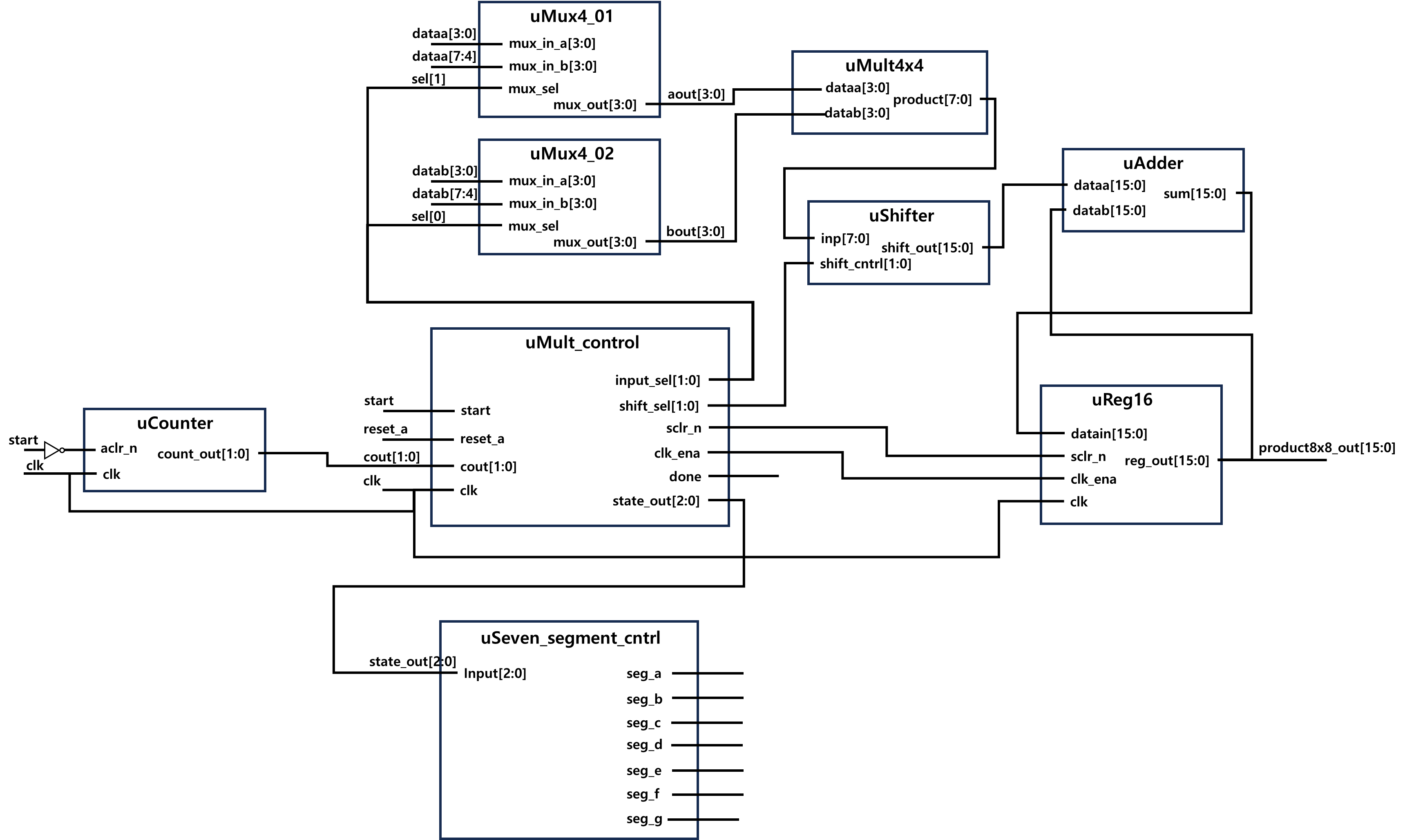

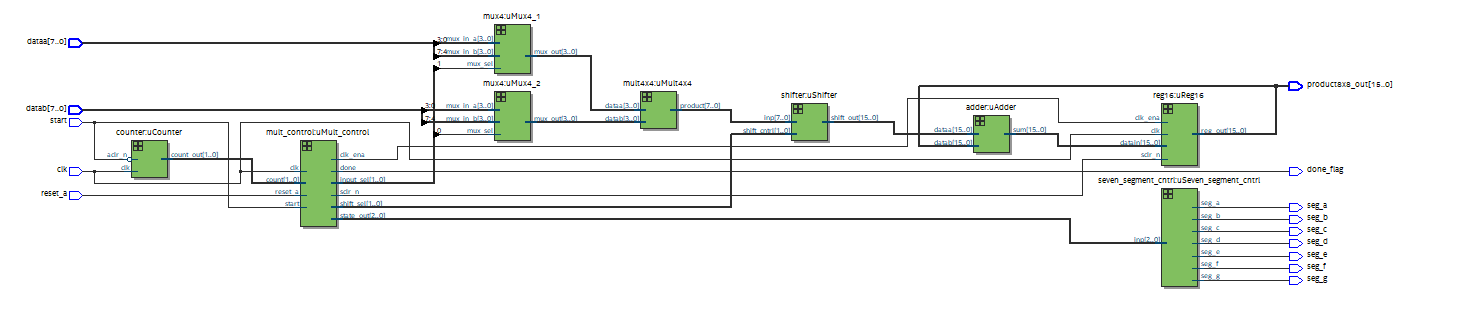

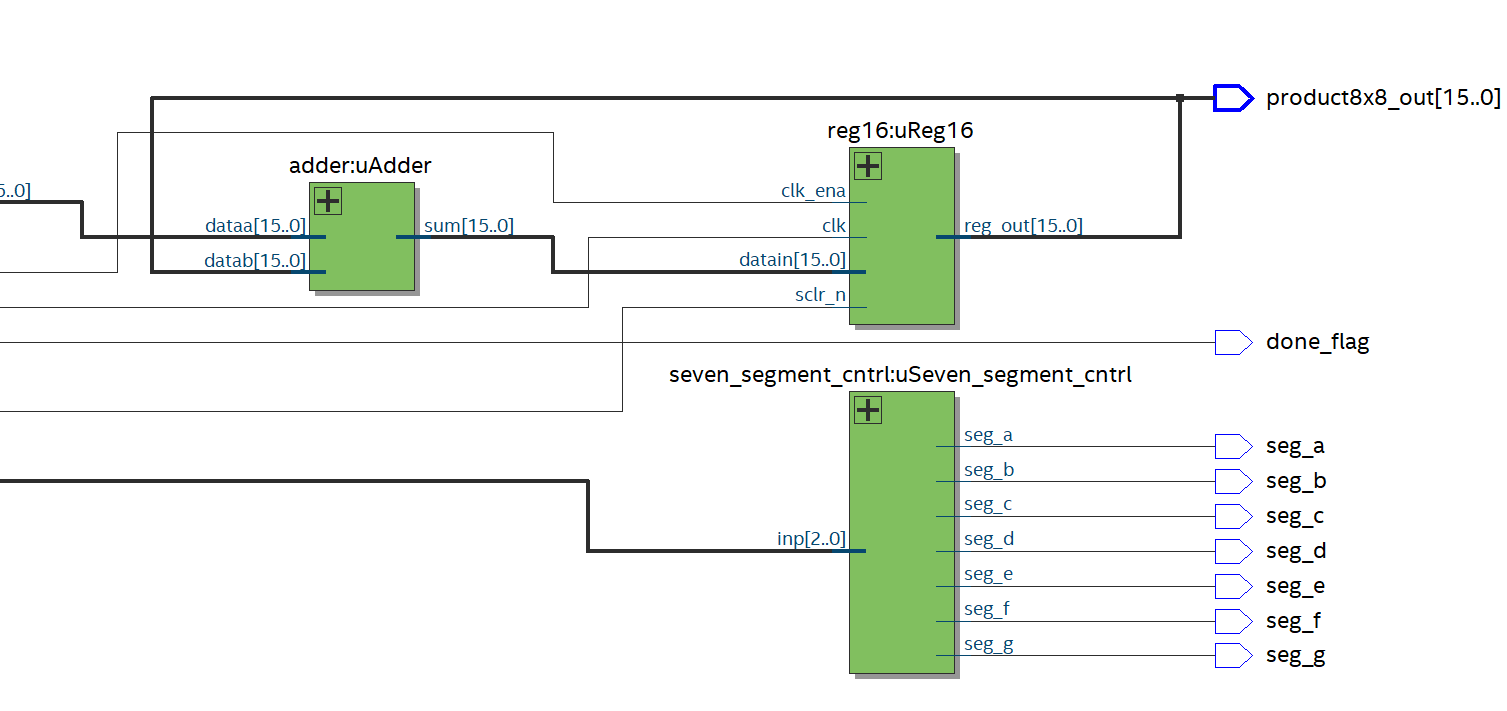

mult 8x8

`include "../lab1a/adder.v"

`include "../lab1b/mult4x4.v"

`include "../lab2a/mux4.v"

`include "../lab2b/shifter.v"

`include "../lab3/seven_segment_cntrl.v"

`include "../lab4a/reg16.v"

`include "../lab4b/counter.v"

`include "../lab5a/mult_control.v"

module mult8x8 (

input [7:0] dataa ,

input [7:0] datab ,

input start ,

input reset_a ,

input clk ,

output done_flag ,

output [15:0] product8x8_out ,

output seg_a ,

output seg_b ,

output seg_c ,

output seg_d ,

output seg_e ,

output seg_f ,

output seg_g

);

wire [1:0] w_count_out ;

wire [1:0] w_sel ;

wire [1:0] w_shift ;

wire [2:0] w_state_out ;

wire [3:0] w_aout ;

wire [3:0] w_bout ;

wire [7:0] w_product ;

wire [15:0] w_shift_out ;

wire [15:0] w_sum ;

counter uCounter(

.clk (clk ),

.aclr_n (~start ),

.count_out (w_count_out )

);

mult_control uMult_control (

.clk (clk ),

.reset_a (reset_a ),

.start (start ),

.count (w_count_out),

.input_sel (w_sel ),

.shift_sel (w_shift ),

.state_out (w_state_out),

.done (done_flag ),

.clk_ena (clk_ena ),

.sclr_n (sclr_n )

);

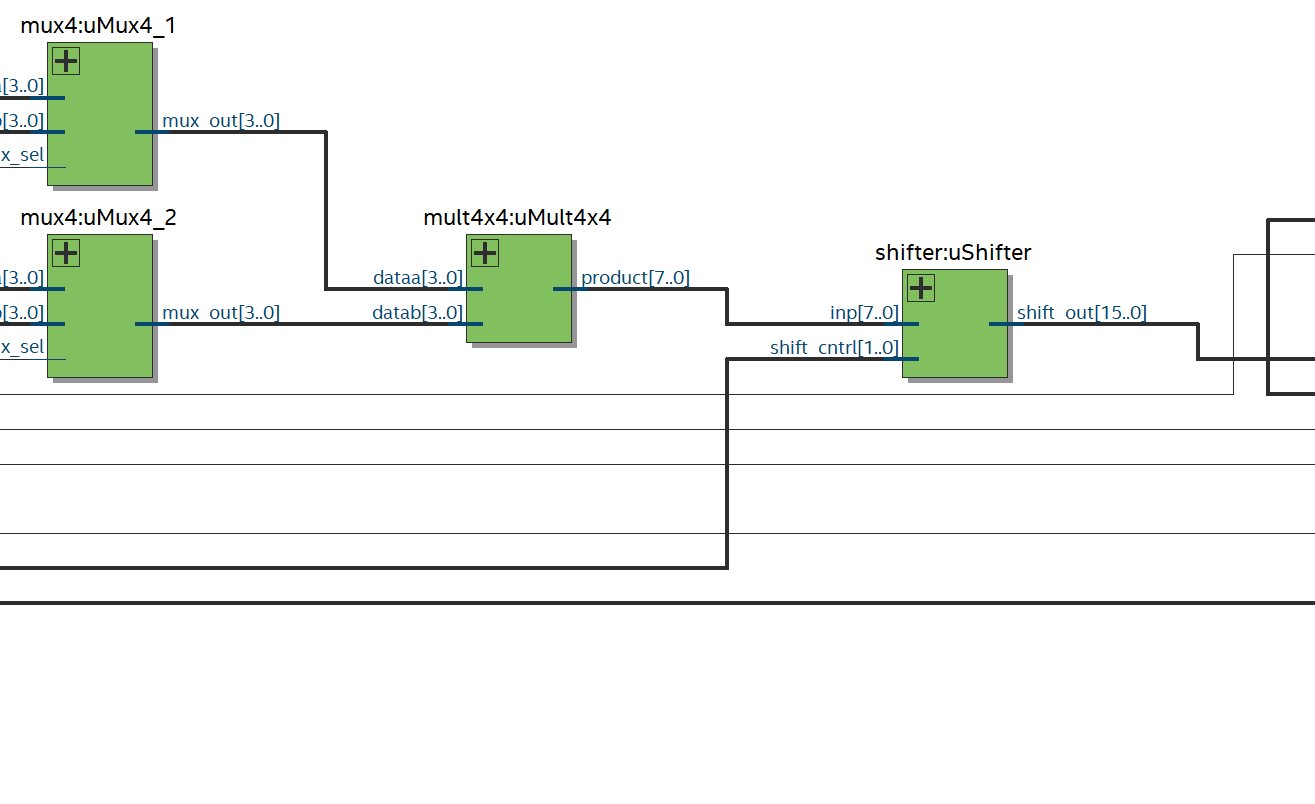

mux4 uMux4_1(

.mux_in_a(dataa[3:0]),

.mux_in_b(dataa[7:4]),

.mux_sel (w_sel[1] ),

.mux_out (w_aout )

);

mux4 uMux4_2(

.mux_in_a(datab[3:0]),

.mux_in_b(datab[7:4]),

.mux_sel (w_sel[0] ),

.mux_out (w_bout )

);

mult4x4 uMult4x4(

.dataa (w_aout ),

.datab (w_bout ),

.product(w_product )

);

shifter uShifter(

.inp (w_product ),

.shift_cntrl(w_shift ),

.shift_out (w_shift_out)

);

reg16 uReg16(

.clk (clk ),

.sclr_n (sclr_n ),

.clk_ena(clk_ena ),

.datain (w_sum ),

.reg_out(product8x8_out )

);

adder uAdder(

.dataa (w_shift_out ),

.datab (product8x8_out),

.sum (w_sum )

);

seven_segment_cntrl uSeven_segment_cntrl(

.inp (w_state_out),

.seg_a(seg_a ),

.seg_b(seg_b ),

.seg_c(seg_c ),

.seg_d(seg_d ),

.seg_e(seg_e ),

.seg_f(seg_f ),

.seg_g(seg_g )

);

endmodule

728x90

'[Harman] 하만 반도체 설계 > VerilogHDL' 카테고리의 다른 글

| Day24. Simple UART RX (0) | 2023.07.28 |

|---|---|

| Day23. Simple UART TX,7-seg button&clock (0) | 2023.07.28 |

| Day21. 4bit 7-segment, 16bit register, 2bit Counter (0) | 2023.07.28 |

| Day20. 7-segment (0) | 2023.07.28 |

| Day19. Function Counter (0) | 2023.07.28 |