Kraklog

Day20. 7-segment 본문

728x90

프로그램 : Quaturs Prime lite edition 18.1

사용문법 : Verilog 2001

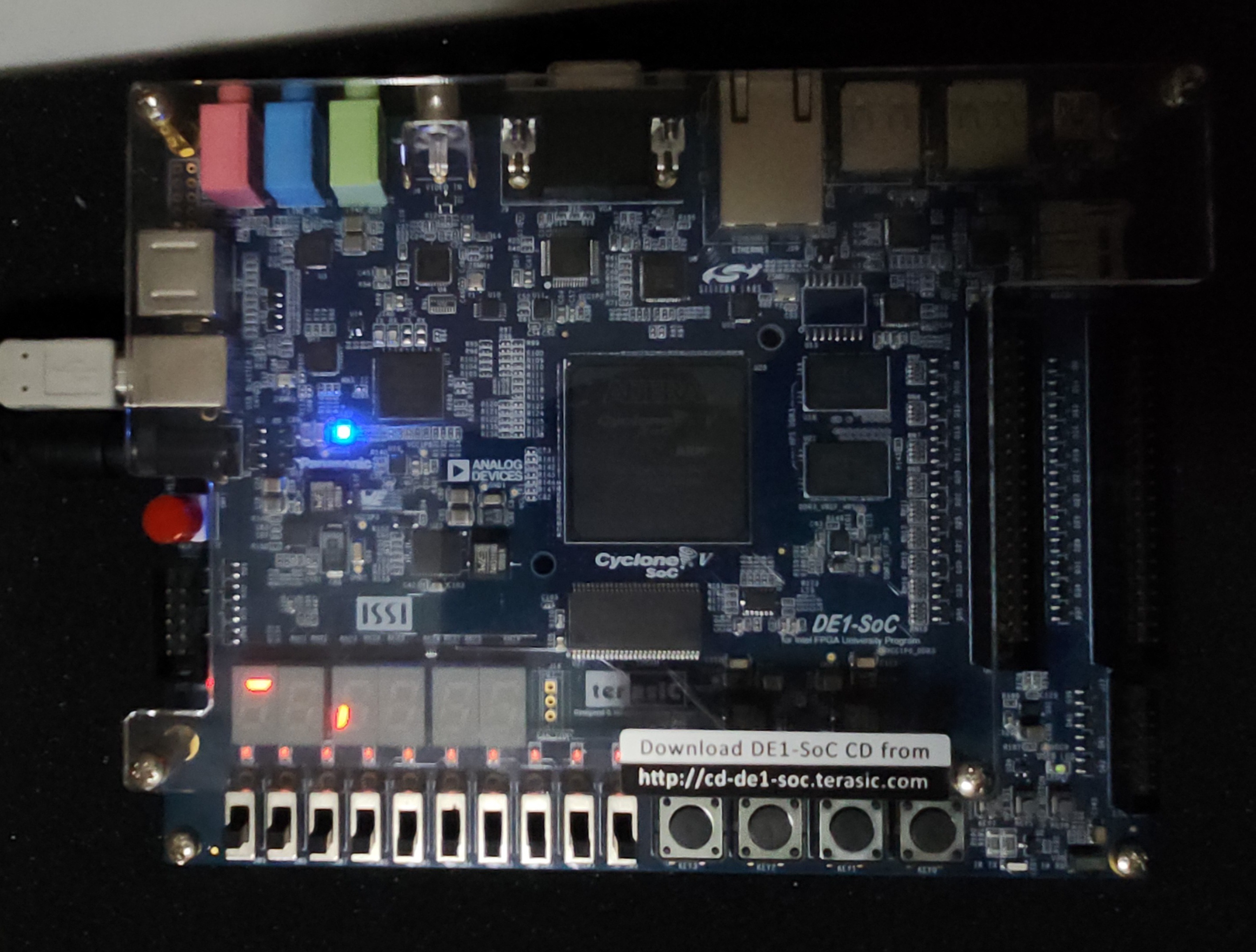

보드 : DE1-SOC

module seven_segment_cntrl (

input [2:0] inp ,

output reg seg_a ,

output reg seg_b ,

output reg seg_c ,

output reg seg_d ,

output reg seg_e ,

output reg seg_f ,

output reg seg_g

);

always @(*) begin

case (inp) //if displayed to segment, add '~' in front of 7'000_0000 for invert it.

3'b000 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = 7'b111_1110;

3'b001 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = 7'b011_0000;

3'b010 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = 7'b110_1101;

3'b011 : {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = 7'b111_1001;

default: {seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g} = 7'b100_1111;

endcase

end

endmodule

module tb_seven_segment_cntrl ();

reg [2:0] inp ;

wire seg_a ;

wire seg_b ;

wire seg_c ;

wire seg_d ;

wire seg_e ;

wire seg_f ;

wire seg_g ;

seven_segment_cntrl uSeven_segment_cntrl(

.inp (inp ),

.seg_a (seg_a),

.seg_b (seg_b),

.seg_c (seg_c),

.seg_d (seg_d),

.seg_e (seg_e),

.seg_f (seg_f),

.seg_g (seg_g)

);

initial begin

inp = 3'd0;

forever

#50 inp = inp + 1;

end

endmodule

처음 7-segment를 다룰 떄 BCD 컨트롤러 라고 선언을 해줬는데, 왜 BCD인지 몰랐었다. (링크)

Segment는 캐소드, 애노드 방식에 따라 데이터 값을 다르게 주어야 하는데, 처음 사진과 같이 코드를 짜주면 원하는 숫자를 제외한 LED에 빛이 들어온다. 따라서 데이터 값을 반전해줄 필요가 있었다.

728x90

'[Harman] 하만 반도체 설계 > VerilogHDL' 카테고리의 다른 글

| Day22. mult control, multiplexer 8x8 (0) | 2023.07.28 |

|---|---|

| Day21. 4bit 7-segment, 16bit register, 2bit Counter (0) | 2023.07.28 |

| Day19. Function Counter (0) | 2023.07.28 |

| Day18. my_rotate (0) | 2023.07.28 |

| Day17. Mux4, Shifter (0) | 2023.07.25 |