Kraklog

Day24. Simple UART RX 본문

728x90

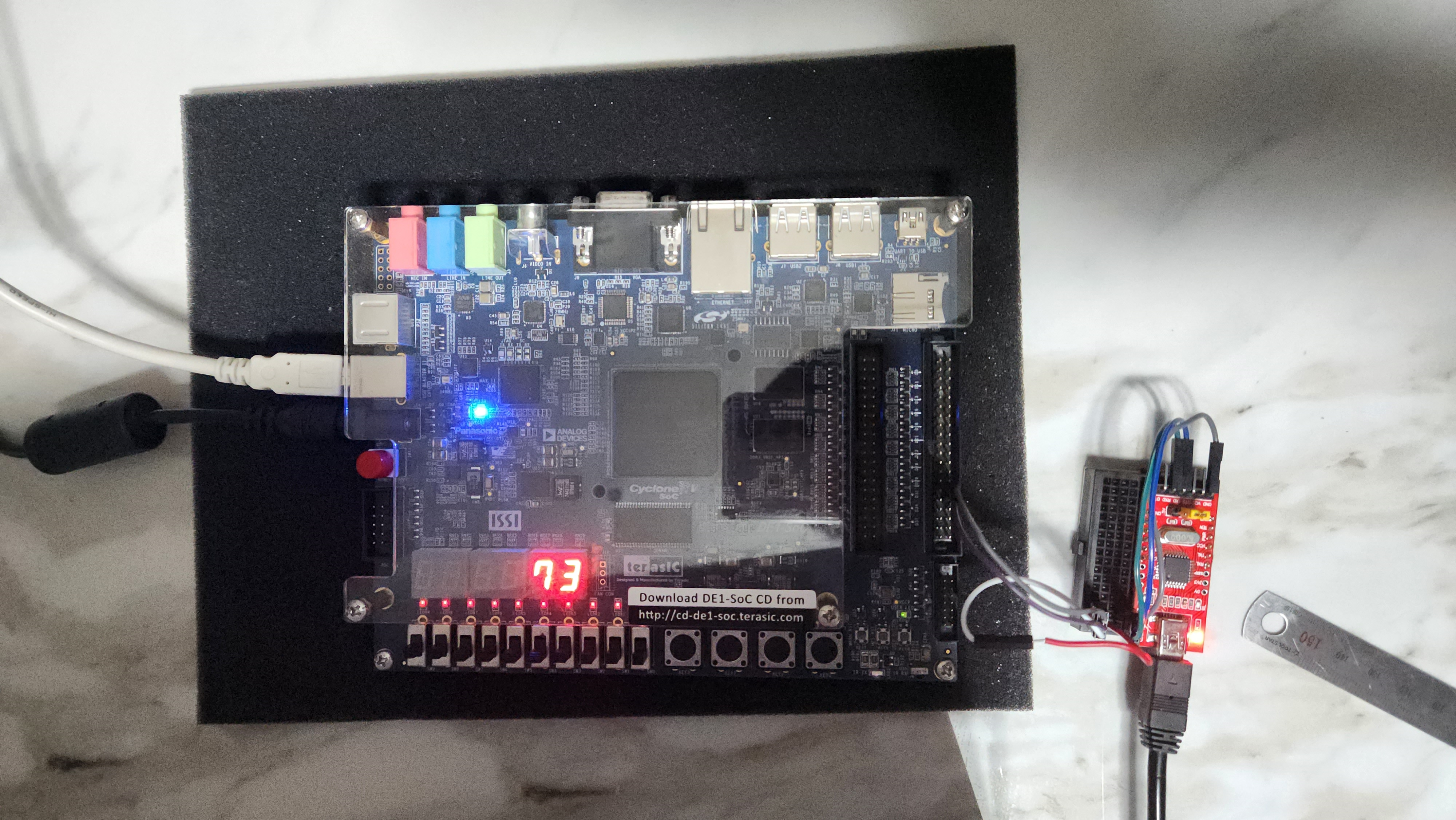

프로그램 : Quaturs Prime lite edition 18.1

사용문법 : Verilog 2001

보드 : DE1-SOC

module simple_uart_rx (

input clk ,

input reset_n ,

input rx ,

output reg [7:0] rx_data

);

// rx falling edge detect

reg rx_delay1;

reg rx_delay2;

wire f_edge_det = !rx_delay1 & rx_delay2;

always @(posedge clk, negedge reset_n) begin

if (!reset_n) begin

rx_delay1 <= 1'b0;

rx_delay2 <= 1'b0;

end

else begin

rx_delay1 <= rx;

rx_delay2 <= rx_delay1;

end

end

parameter IDLE=0, START=1, MID=2, D0=3, D1=4, D2=5, D3=6, D4=7, D5=8, D6=9, D7=10, STOP=11;

reg [8:0] cnt;

reg [3:0] cst, nst;

wire bit_clr = (cnt == 433);

wire bit_clr_h = (cnt == 216) && (cst == START);

// wire bit_clr_det = (f_edge_det) && (cst == IDLE); // replace (IDLE state) => cnt = 0

// counter

always @(posedge clk, negedge reset_n) begin

if (!reset_n) cnt <= 9'd0;

else if (bit_clr||bit_clr_h||cst == IDLE) cnt <= 9'd0;

else cnt <= cnt + 9'd1;

end

// state register

always @(posedge clk, negedge reset_n) begin

if (!reset_n) cst <= IDLE;

else cst <= nst;

end

// next state combinational logic

always @(*) begin

case (cst)

START : if (bit_clr_h) nst = MID; else nst = START;

MID : if (bit_clr) nst = D0; else nst = MID;

D0 : if (bit_clr) nst = D1; else nst = D0;

D1 : if (bit_clr) nst = D2; else nst = D1;

D2 : if (bit_clr) nst = D3; else nst = D2;

D3 : if (bit_clr) nst = D4; else nst = D3;

D4 : if (bit_clr) nst = D5; else nst = D4;

D5 : if (bit_clr) nst = D6; else nst = D5;

D6 : if (bit_clr) nst = D7; else nst = D6;

D7 : if (bit_clr) nst = STOP; else nst = D7;

STOP : if (bit_clr) nst = IDLE; else nst = STOP;

default : if (f_edge_det) nst = START; else nst = IDLE;

endcase

end

// output combinational logic

always @(posedge clk, negedge reset_n) begin

if (!reset_n) rx_data = 8'd0;

else if (cnt == 0) begin

case (cst)

D0 : rx_data[0] = rx;

D1 : rx_data[1] = rx;

D2 : rx_data[2] = rx;

D3 : rx_data[3] = rx;

D4 : rx_data[4] = rx;

D5 : rx_data[5] = rx;

D6 : rx_data[6] = rx;

D7 : rx_data[7] = rx;

endcase

end

end

endmodulemodule simple_uart_rx_top (

input clk ,

input reset_n ,

input rx ,

output seg_a ,

output seg_b ,

output seg_c ,

output seg_d ,

output seg_e ,

output seg_f ,

output seg_g ,

output seg_h ,

output seg_i ,

output seg_j ,

output seg_k ,

output seg_l ,

output seg_m ,

output seg_n

);

wire [7:0] w_rx_data;

simple_uart_rx uSimple_uart_rx_0(

.clk (clk ) ,

.reset_n (reset_n ) ,

.rx (rx ) ,

.rx_data (w_rx_data )

);

seven_segment_cntrl uSeven_segment_cntrl_0 (

.inp (w_rx_data[3:0]) ,

.seg_a (seg_a ) ,

.seg_b (seg_b ) ,

.seg_c (seg_c ) ,

.seg_d (seg_d ) ,

.seg_e (seg_e ) ,

.seg_f (seg_f ) ,

.seg_g (seg_g )

);

seven_segment_cntrl uSeven_segment_cntrl_1 (

.inp (w_rx_data[7:4]) ,

.seg_a (seg_h ) ,

.seg_b (seg_i ) ,

.seg_c (seg_j ) ,

.seg_d (seg_k ) ,

.seg_e (seg_l ) ,

.seg_f (seg_m ) ,

.seg_g (seg_n )

);

endmodule

728x90

'[Harman] 하만 반도체 설계 > VerilogHDL' 카테고리의 다른 글

| Day.79 Advanced Verilog #2 (0) | 2023.11.10 |

|---|---|

| Day.78 Advanced Verilog #1-원치 않는 Latch 제거 (0) | 2023.11.09 |

| Day23. Simple UART TX,7-seg button&clock (0) | 2023.07.28 |

| Day22. mult control, multiplexer 8x8 (0) | 2023.07.28 |

| Day21. 4bit 7-segment, 16bit register, 2bit Counter (0) | 2023.07.28 |