Kraklog

[Verilog_LAB3] Part1 본문

728x90

프로그램 : Quaturs Prime lite edition 18.1

사용문법 : Verilog 2001

보드 : DE1-SOC

설계목표 : RS래치 생

`define LU2

module part1 (

input clk ,

input R ,

input S ,

`ifdef LU

output reg Q

`elsif LU2

output Q

`else

output Q

`endif

);

`ifdef LU

always @* begin

case ({clk & R,clk & S})

2'b00: Q = Q;

2'b01: Q = 1'b0;

2'b10: Q = 1'b1;

2'b11: Q = 1'bz;

default: Q = 1'bz;

endcase

end

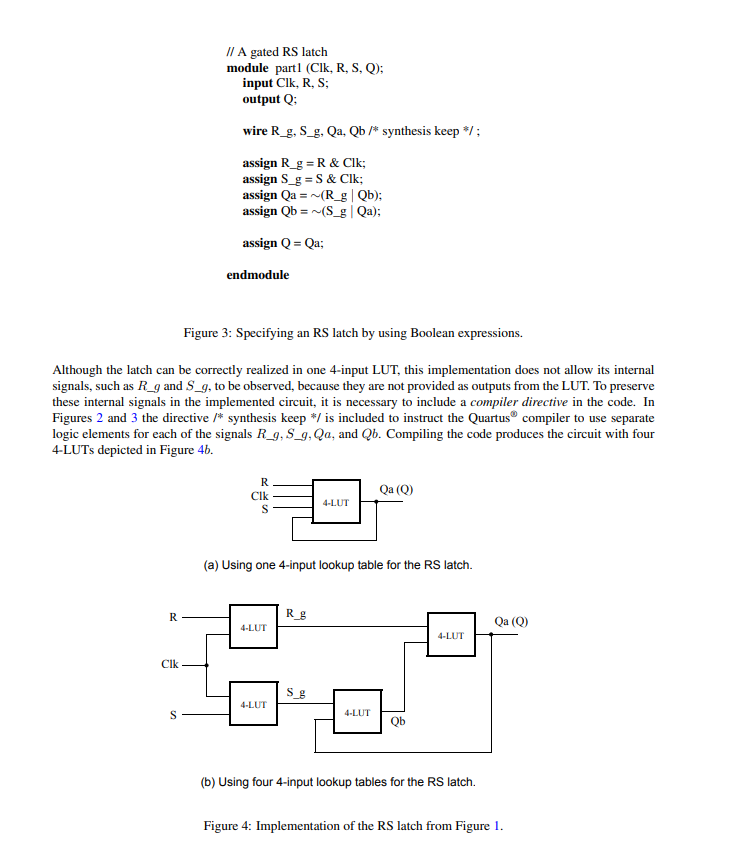

`elsif LU2

wire R_g, S_g, Qa, Qb;

assign R_g = clk & R;

assign S_g = clk & S;

assign Qa = ~(R_g | Qb);

assign Qb = ~(S_g | Qa);

assign Q = Qa;

`else

wire R_g, S_g, Qa, Qb/* synthesis keep*/;

and and_0 (R_g, R, clk);

and and_1 (S_g, S, clk);

nor nor_0 (Qa, R_g, Qb);

nor nor_1 (Qb, S_g, Qa);

assign Q= Qa;

`endif

endmodule`timescale 1ns / 1ns

module tb_part1 ();

reg clk;

reg R;

reg S;

wire Q;

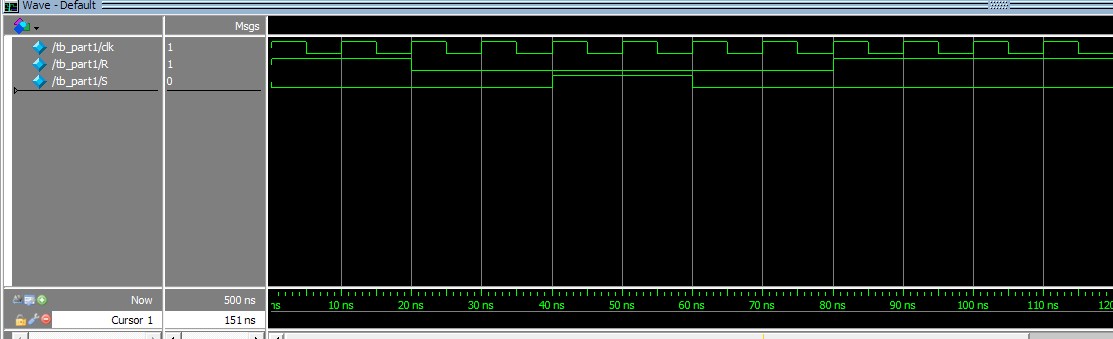

initial

begin: CLOCK_GENERATOR

clk = 1;

forever

begin

#5 clk = ~clk;

end

end

initial

begin

R <= 1; S <= 0;

#20 R <= 0;

#20 S <= 1;

#20 S <= 0;

#20 R <= 1;

end

part1 p1 (

.clk,

.R,

.S,

.Q

);

endmodule

728x90

'[Harman] 하만 반도체 설계 > CPU설계' 카테고리의 다른 글

| [Verilog_LAB3] Part3 (0) | 2023.12.19 |

|---|---|

| [Verilog_LAB3] Part2 (0) | 2023.12.19 |

| [Verilog_LAB2] Part6 (0) | 2023.12.19 |

| [Verilog_LAB2] Part5 (1) | 2023.12.19 |

| [Verilog_LAB2] Part4 (0) | 2023.12.19 |