Kraklog

[Verilog_LAB3] Part3 본문

728x90

프로그램 : Quaturs Prime lite edition 18.1

사용문법 : Verilog 2001

보드 : DE1-SOC

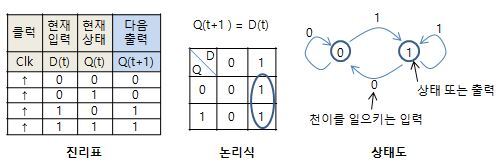

설계 목표 : D 플립 플롭 (master slave)

module part3 (

input clk,

input [1:0] SW,

output LEDR

);

reg Qm;

reg Qs;

always @(posedge ~clk) begin

Qm <= SW;

end

always @(posedge clk) begin

Qs <= Qm;

end

assign LEDR = ~Qs;

endmodule

module part3 (

input clk,

input [1:0] SW,

output LEDR

);

reg Qm;

reg Qs;

always @(posedge ~clk) begin

Qm <= SW;

end

always @(posedge clk) begin

Qs <= Qm;

end

assign LEDR = ~Qs;

endmodule

module part3 (

input [1:0] SW,

output LEDR

);

wire Qm;

wire Qs;

wire clk =SW[1];

wire D = SW[0];

D_latch u0 (

.clk (~clk),

.D(D),

.Q(Qm)

);

D_latch u1 (

.clk (clk),

.D(Qm),

.Q(Qs)

);

assign LEDR =Qs;

endmodule

728x90

'[Harman] 하만 반도체 설계 > CPU설계' 카테고리의 다른 글

| [Verilog_LAB3] Part5 (0) | 2023.12.19 |

|---|---|

| [Verilog_LAB3] Part4 (0) | 2023.12.19 |

| [Verilog_LAB3] Part2 (0) | 2023.12.19 |

| [Verilog_LAB3] Part1 (0) | 2023.12.19 |

| [Verilog_LAB2] Part6 (0) | 2023.12.19 |