Kraklog

[Verilog_LAB2] Part4 본문

728x90

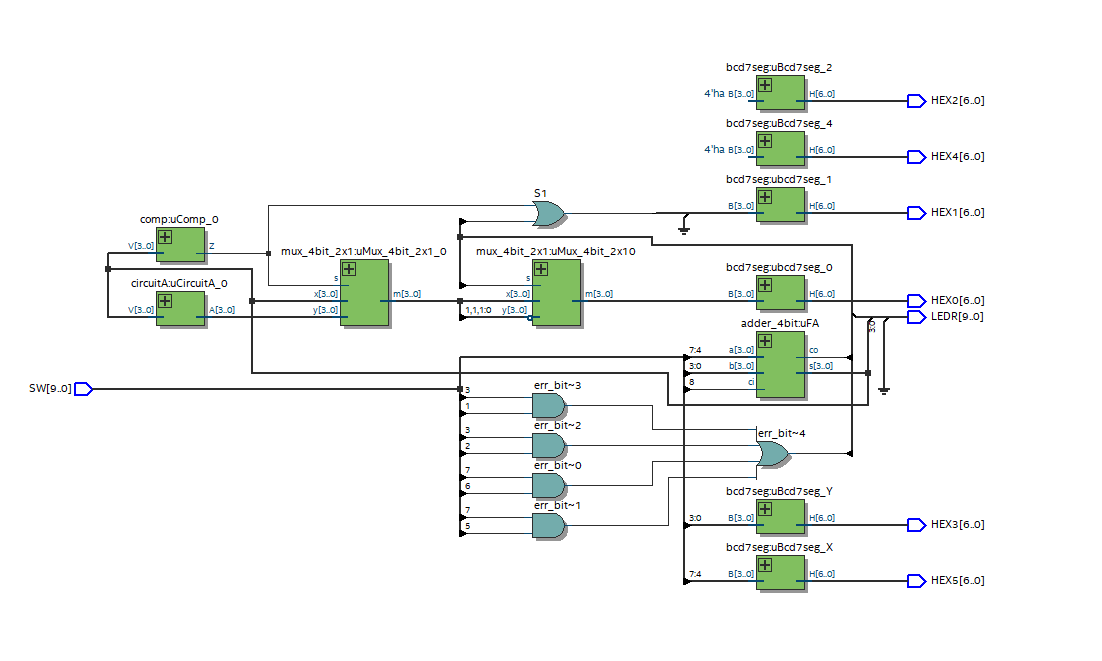

프로그램 : Quaturs Prime lite edition 18.1

사용문법 : Verilog 2001

보드 : DE1-SOC

설계목표 : PartII(2023.12.19 - [[Harman] 하만 반도체 설계/CPU설계] - [Verilog_LAB2] Part2) 에서 사용한 Full adder를 이용해서 segment에 덧셈을 표현. LED 가장 우측(LED9)에 error bit를 표현한다.

`define BUS_SIZE 2

`define SL_SIZE 10 //switch LED size

`define SEG7_WD 7

module part4(

input [`SL_SIZE-1:0] SW ,

output [`SL_SIZE-1:0] LEDR ,

output [`SEG7_WD-1:0] HEX0 ,

output [`SEG7_WD-1:0] HEX1 ,

output [`SEG7_WD-1:0] HEX2 ,

output [`SEG7_WD-1:0] HEX3 ,

output [`SEG7_WD-1:0] HEX4 ,

output [`SEG7_WD-1:0] HEX5

);

wire [3:0] X;

wire [3:0] Y;

wire err_bit;

assign X = SW[7:4];

assign Y = SW[3:0];

assign err_bit = (X[3] & X[2])|(X[3] & X[1])|

(Y[3] & Y[2])|(Y[3] & Y[1]);

assign LEDR[9] = err_bit;

//assign err_bit = (x>9) | (y>9);

//3210 bit

//1000 : 8

//1001 : 9

//1010 : 10 - err

//1011 : 11 - err

//1100 : 12 - err

//1101 : 13 - err

//1110 : 14 - err

//1111 : 15 - err

//3, 1 bit & / 3, 2 bit & ->

wire [3:0] a = X;

wire [3:0] b = Y;

wire ci = SW[8];

wire [3:0] s;

wire co;

assign LEDR[4:0] = {co,s};

adder_4bit uFA(

.a (a) ,

.b (b) ,

.ci(ci) ,

.s (s) ,

.co(co)

);

wire [3:0] V=s;

wire [3:0] A;

wire [3:0] B1;

wire [3:0] B0;

wire Z;

//wire [`SEG7_WD-1:0] HEX0;

// wire [`SEG7_WD-1:0] HEX1;

wire [`SEG7_WD-1:0] H0;

wire [`SEG7_WD-1:0] H1;

//co3210

//01111 : 15

//10000 : 16

//10001 : 17

//10010 : 18

//10011 : 19

comp uComp_0(

.V(V),

.Z(Z)

);

circuitA uCircuitA_0(

.V(V),

.A(A)

);

mux_4bit_2x1 uMux_4bit_2x1_0(

.x(V),

.y(A),

.s(Z),

.m(B0)

);

//B0 : ~15

//0000 : 16 (occured carry, 16) -> 0000 = 6 (0110)

//0001 : 7 (0111)

//0010 : 8 (1000)

//0011 : 9 (1001)

wire [3:0] B;

wire [3:0] m;

assign B[3] = B0[1]; //0000 -> "0"110

assign B[2] = ~B0[1]; //0000 -> 0"1"10

assign B[1] = ~B0[1]; //0000 -> 01"1"0

assign B[0] = B0[0]; //0000 -> 011"0"

wire S1;

assign S1 = co | Z;

mux_4bit_2x1 uMux_4bit_2x1_0(

.x(B0),

.y(B),

.s(co),

.m(m)

);

//[s1]s0

bcd7seg ubcd7seg_1(

//.B({3'b000,Z}),

.B({3'b000,S1}),

.H(H1)

);

//s1[s0]

bcd7seg ubcd7seg_0(

//.B(B0),

.B(m),

.H(H0)

);

//todo : do sim

//error : H1 initial value

assign HEX0 = H0;

assign HEX1 = H1;

//turn off HEX2,4

bcd7seg uBcd7seg_4 (

.B(4'b1010),

.H(HEX4)

);

bcd7seg uBcd7seg_2 (

.B(4'b1010),

.H(HEX2)

);

bcd7seg uBcd7seg_X (

.B(X),

.H(HEX5)

);

bcd7seg uBcd7seg_Y (

.B(Y),

.H(HEX3)

);

endmodule`define SL_SIZE 10

`define SEG7_WD 7

module bcd7seg (

input [3:0] B,

output [`SEG7_WD-1:0] H

);

// _0_

// 5|_6__| 1

// 4|_3__| 2

//

reg [`SEG7_WD-1:0] rH;

always @(*)

begin

case (B)

/*

//4'b**** : rH = ~7'b654_3210;

4'b0000 : rH = ~7'b011_1111;

4'b0001 : rH = ~7'b000_0110;

4'b0010 : rH = ~7'b101_1011;

4'b0011 : rH = ~7'b100_1111;

4'b0100 : rH = ~7'b110_0110;

4'b0101 : rH = ~7'b110_1101;

4'b0110 : rH = ~7'b111_1101;

4'b0111 : rH = ~7'b010_0111;

4'b1000 : rH = ~7'b111_1111;

4'b1001 : rH = ~7'b110_0111;

default : rH = ~7'b000_0000;

*/

4'b0000 : rH = ~7'b011_1111;

4'b0001 : rH = ~7'b000_0110;

4'b0010 : rH = ~7'b101_1011;

4'b0011 : rH = ~7'b100_1111;

4'b0100 : rH = ~7'b110_0110;

4'b0101 : rH = ~7'b110_1101;

4'b0110 : rH = ~7'b111_1101;

4'b0111 : rH = ~7'b010_0111;

4'b1000 : rH = ~7'b111_1111;

4'b1001 : rH = ~7'b110_0111;

default : rH = ~7'b000_0000;

endcase

end

assign H = rH;

endmodule*남은 모듈은 이전 발행글의 모듈을 사용

728x90

'[Harman] 하만 반도체 설계 > CPU설계' 카테고리의 다른 글

| [Verilog_LAB2] Part6 (0) | 2023.12.19 |

|---|---|

| [Verilog_LAB2] Part5 (1) | 2023.12.19 |

| [Verilog_LAB2] Part3 (1) | 2023.12.19 |

| [Verilog_LAB2] Part2 (0) | 2023.12.19 |

| [Verilog_LAB2] Part1 (0) | 2023.12.19 |