Kraklog

Day15~16. Verilog 시작 /Adder, 4x4 mult 본문

728x90

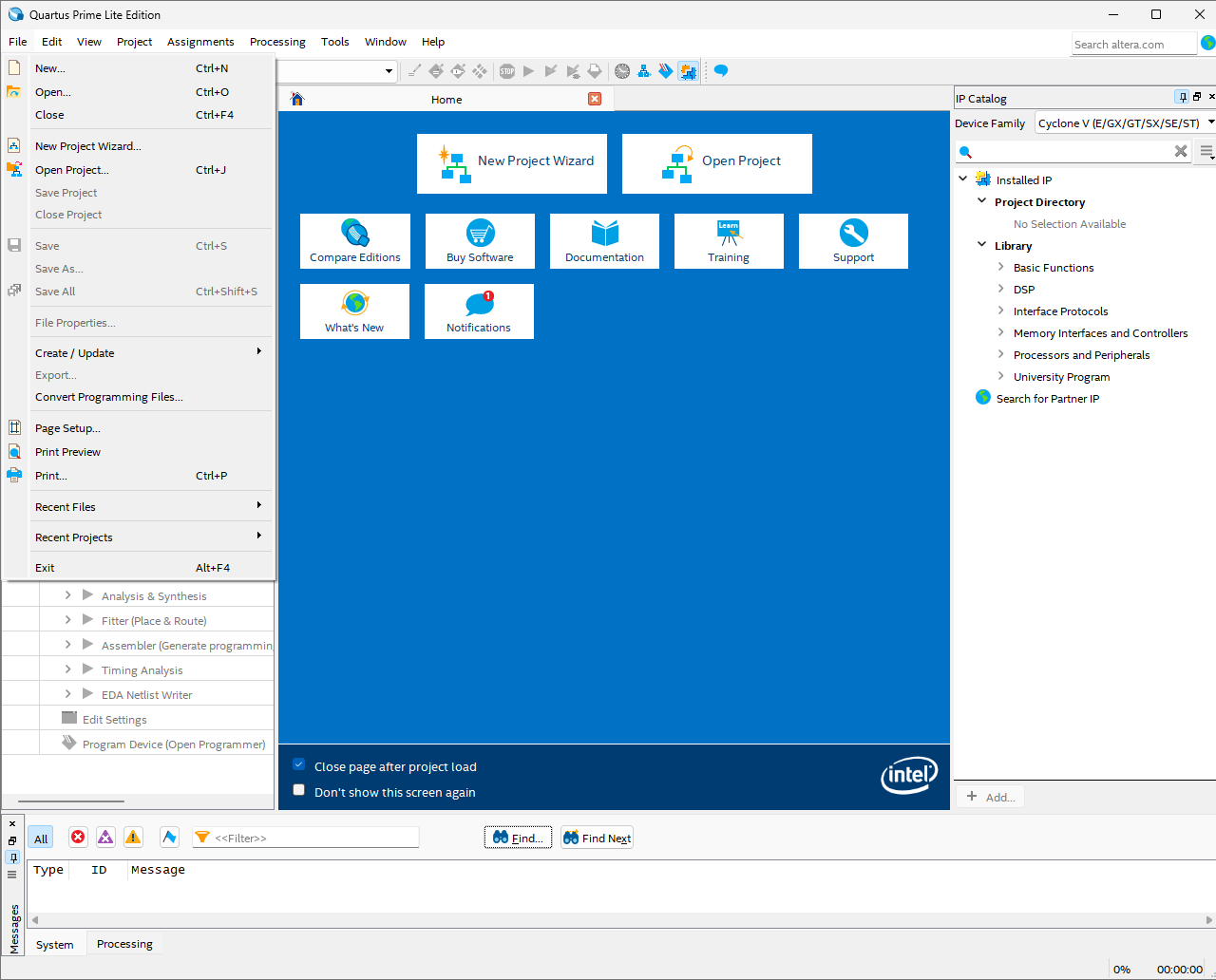

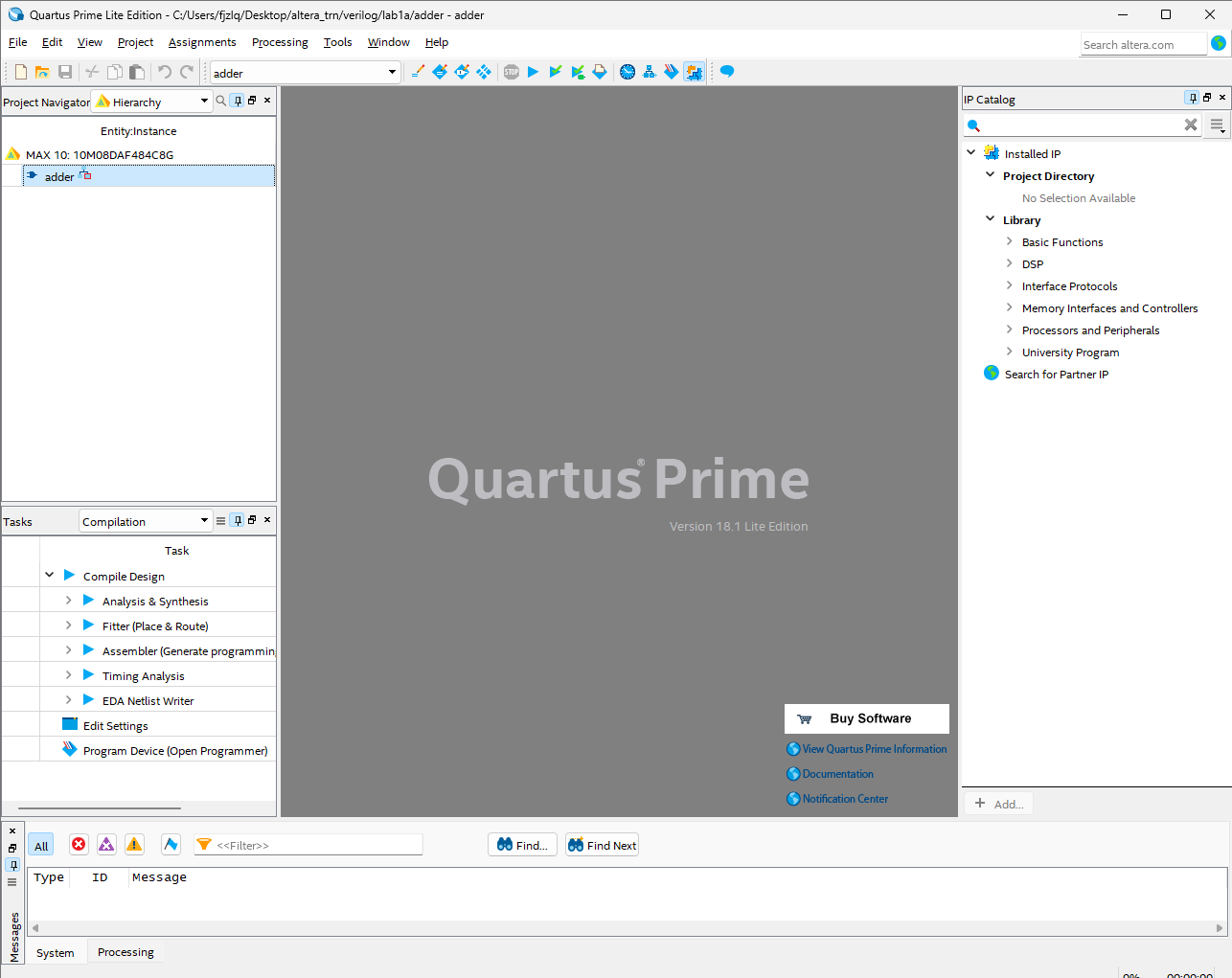

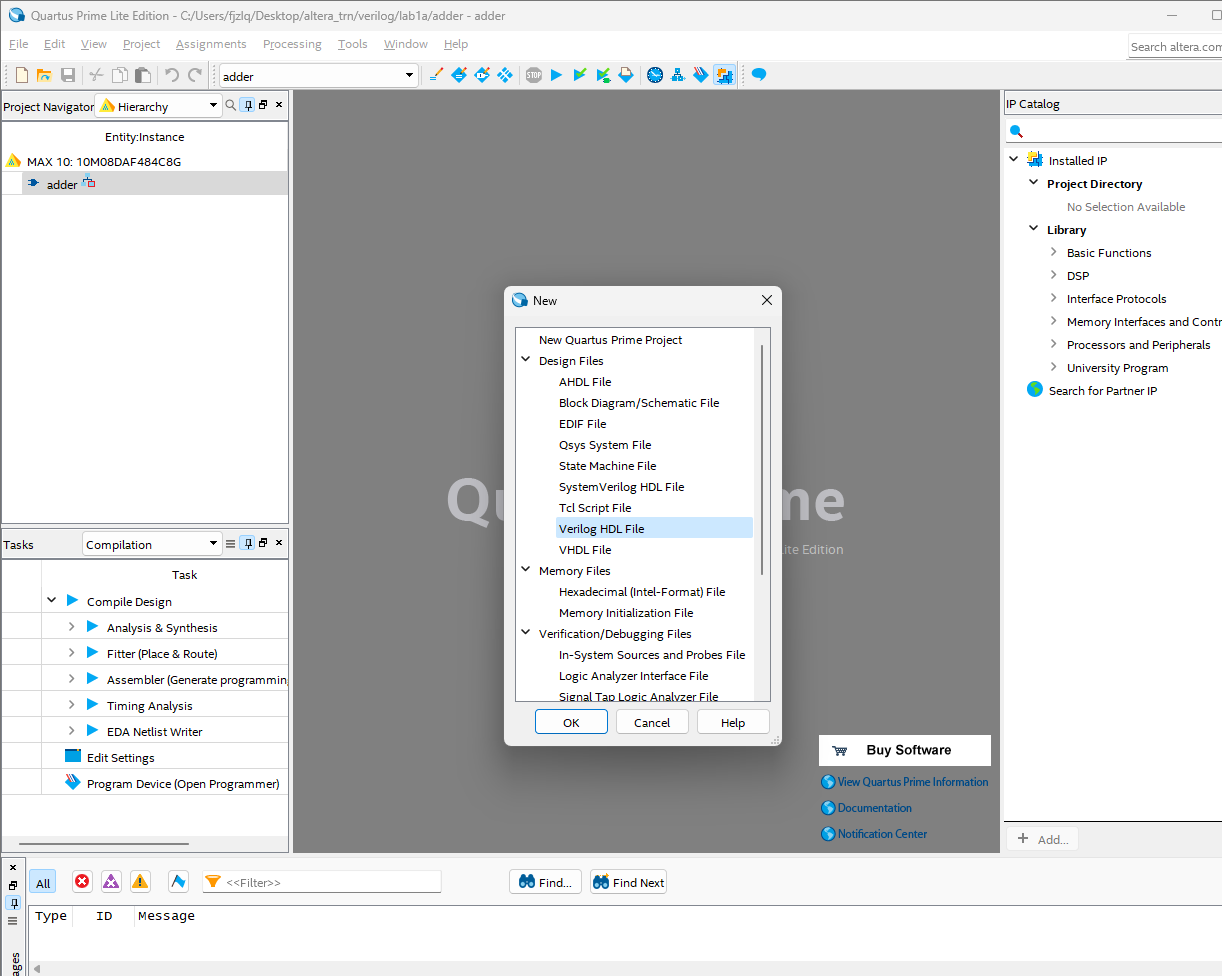

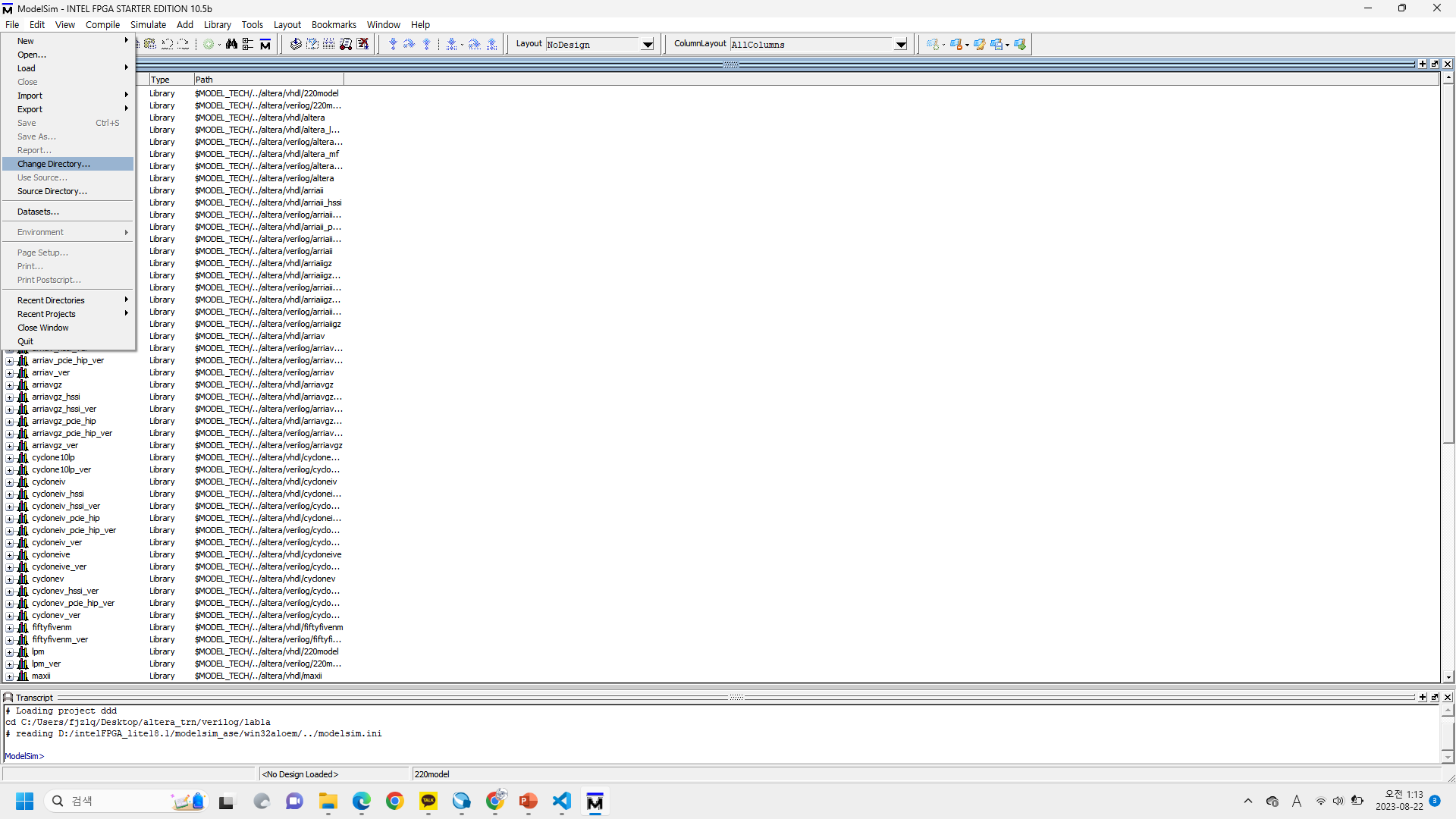

프로그램 : Quaturs Prime lite edition 18.1

사용문법 : Verilog 2001

실습 목표 : 8x8 multiplexer build

8x8 mux를 기본 논리게이트와 컨트롤을 구성하여 처음부터 작성하는것이 현재 최종 목표이다.

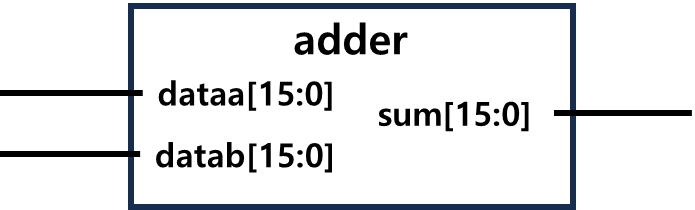

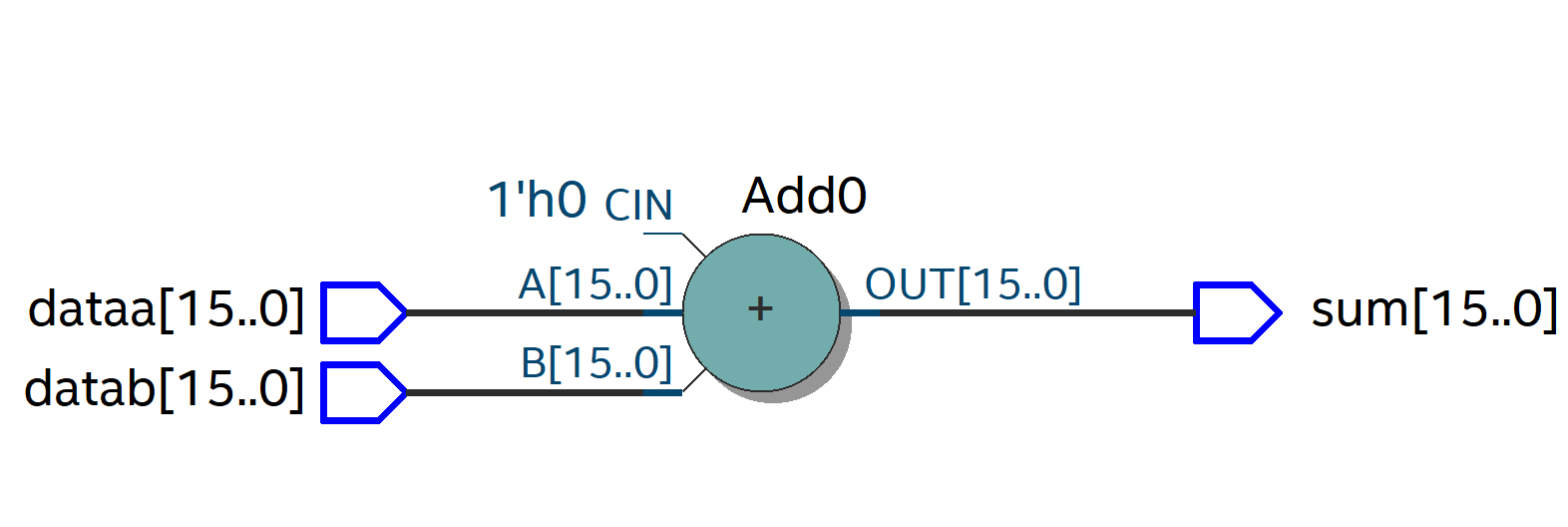

1.Adder

16bit - adder

module adder (

input [15:0] dataa,

input [15:0] datab,

output [15:0] sum

);

assign sum = dataa + datab;

endmodule

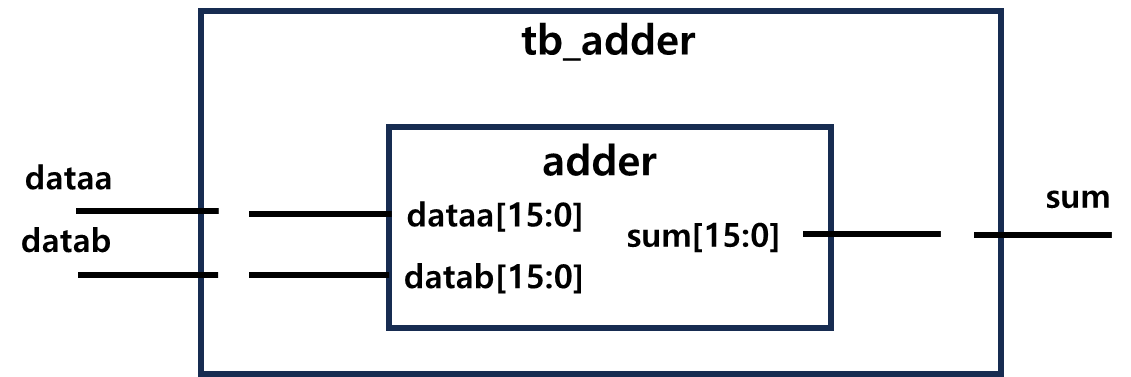

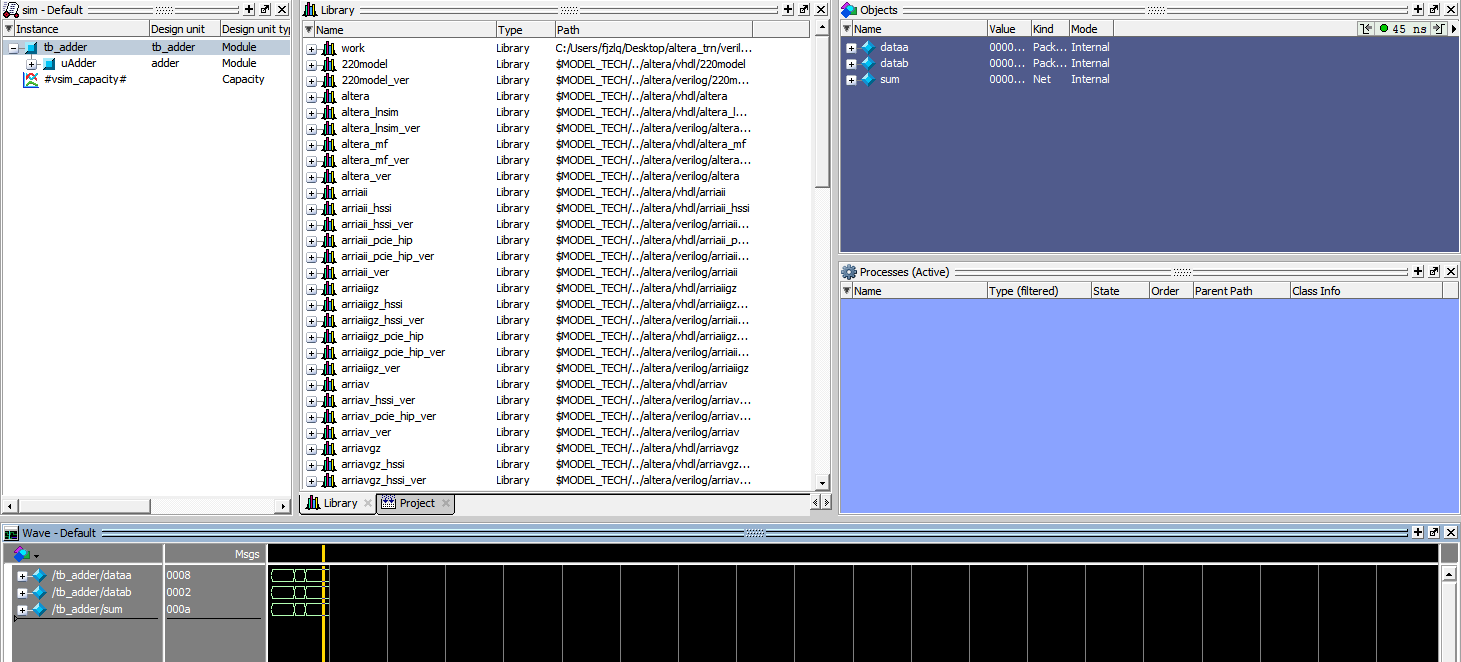

16bit - tb_adder

module tb_adder ();

reg [15:0] dataa ;

reg [15:0] datab ;

wire [15:0] sum ;

adder uAdder (

.dataa(dataa),

.datab(datab),

.sum(sum)

);

initial begin

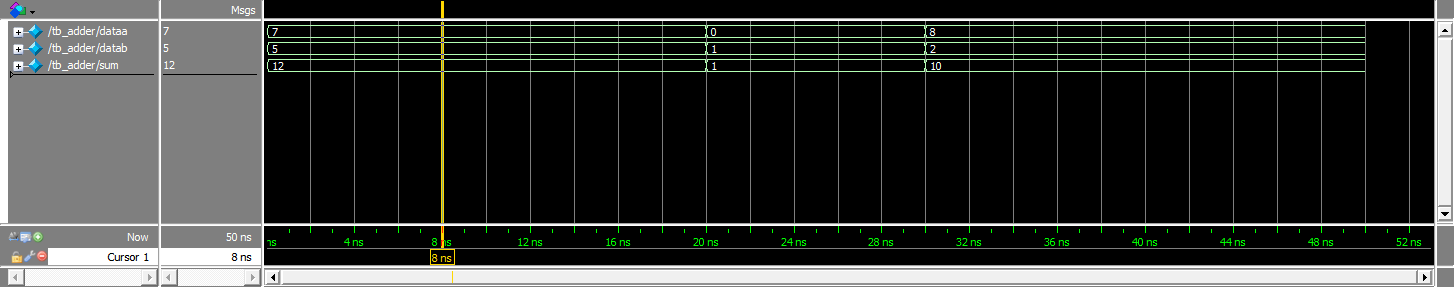

dataa = 16'd7; datab = 16'd5;

#20 dataa = 16'd0; datab = 16'd1;

#10 dataa = 16'd8; datab = 16'd2;

end

endmodule

입력 값 A, B에 따라 덧셈 결과인 값이 제대로 출력 됨을 알 수 있다.

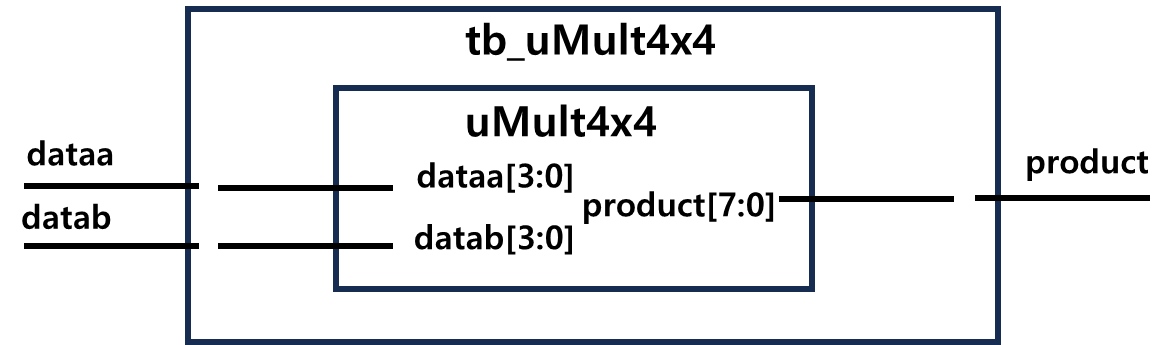

4x4 mult

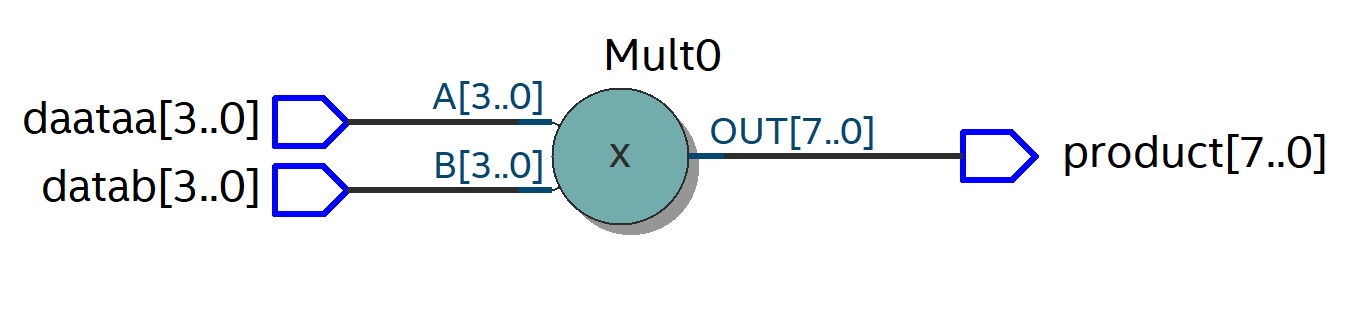

module mult4x4 (

input [3:0] dataa ,

input [3:0] datab ,

output [7:0] product

);

assign product = dataa * datab;

endmodule

module tb_mult4x4 ();

reg [3:0] dataa ;

reg [3:0] datab ;

wire [7:0] product ;

mult4x4 uMult4x4(

.dataa(dataa),

.datab(datab),

.product(product)

);

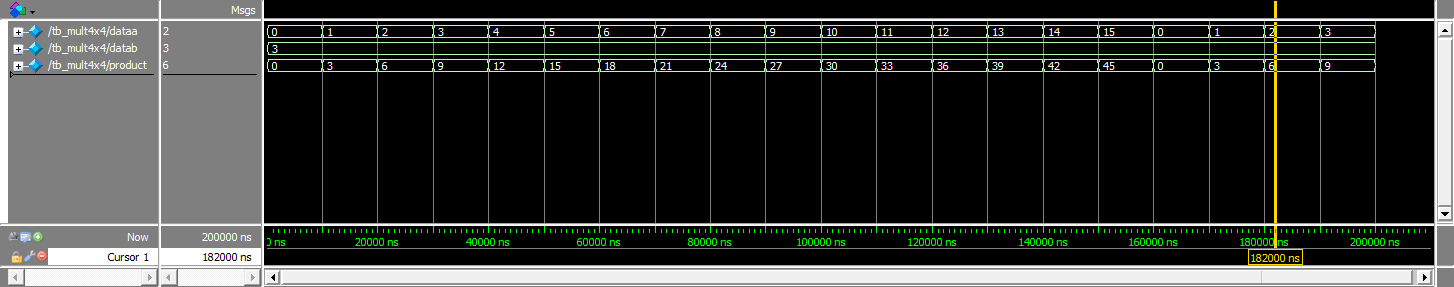

initial begin

dataa = 4'd0;

datab = 4'd3;

forever

#10 dataa = dataa + 1;

end

endmodule

테스트 벤치상 dataB를 3으로 고정, dataA의 입력값의 변화에 따라 곱셉 값을 출력 받음을 알 수 있다.

728x90

'[Harman] 하만 반도체 설계 > VerilogHDL' 카테고리의 다른 글

| Day21. 4bit 7-segment, 16bit register, 2bit Counter (0) | 2023.07.28 |

|---|---|

| Day20. 7-segment (0) | 2023.07.28 |

| Day19. Function Counter (0) | 2023.07.28 |

| Day18. my_rotate (0) | 2023.07.28 |

| Day17. Mux4, Shifter (0) | 2023.07.25 |