Kraklog

플립플롭 본문

1. 플립플롭

조합논리회로는 현재 입력의 조합에 의해 출력이 결정된다.

하지만 순서논리회로에서는 현재 입력의 조합과 입력이 인가되는 시점의 회로의 상태 (High/Low)에 영향을 받아 출력이 결정된다.

따라서 순서논리회로에서는 회로의 상태를 기억하는 기억소자가 필요하다.

기억소자의 대표적은 다음과 같다 : 플립플롭(flip-flop), 래치(latch), 쌍안정(bi-stable) 이며 1비트 기억소자들이다.

플립플롭에는 SR D JK T가 있지만 JK가 가장 많이 쓰인다.

SR플립플롭의 결점을 개선한것이 JK이며, D와 T 플립플롭의 동작은 SR과 JK플립플롭으로 부터 나타낼 수 있다.

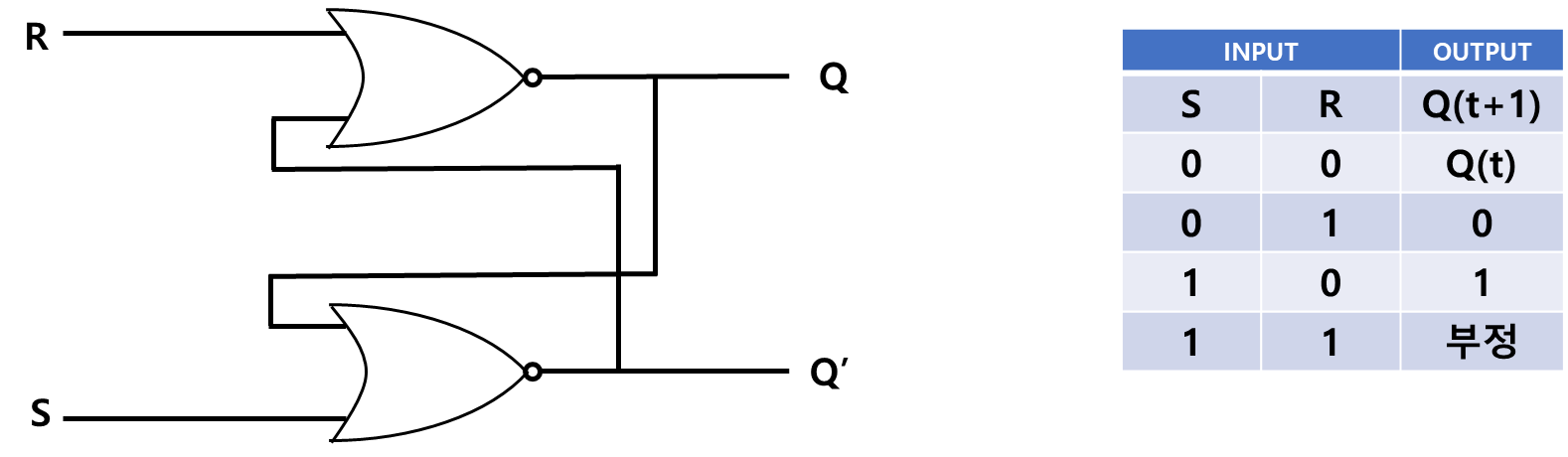

기본적인 플립플롭 회로는 NAND나 NOR을 통해 얻을 수 있는데 NOR게이트 래치, NAND게이트 래치 라고 부른다.

NOR게이트 혹은 NAND 게이트 연결은 한 게이트의 출력이 다른 게이트의 입력이 되는 서로 교차 결합 형태의 쌍안정 회로이며, 서로 선이 교차되는 궤환 구성을 이루고있다.

SR래치는 Set과 Reset의 입력을 갖고 있으며 Q와 Q'로 표시된 2개의 출력을 갖고 있다.

이때 Q와 Q'는 서로 보수 상태가 되어야 정상 상태가 된다.

플립플롭은 논리게이트와 비슷하지만 다른 특성을 갖는데, 예를 들면 지연 시간이 있다.

ideal적인 상황에서는 High ~ Low로 변하는 시간이 0초가 되겠지만, 실제는 물리적인 한계로 인해 지연시간이 발생한다.

따라서 플립플롭이 안정적인 (내가 설계한 값이 ) 출력 값을 갖도록 하기 위해선 일정 시간 동작을 하게 만들어야 하며, 이것을 설정시간이라고 한다.

또한, 신뢰성이 있는 동작을 가능하도록 하기 위해 유지시간이 필요한데, 클럭신호가 바뀐 후에도 일정시간 출력을 유지시켜야 한다.

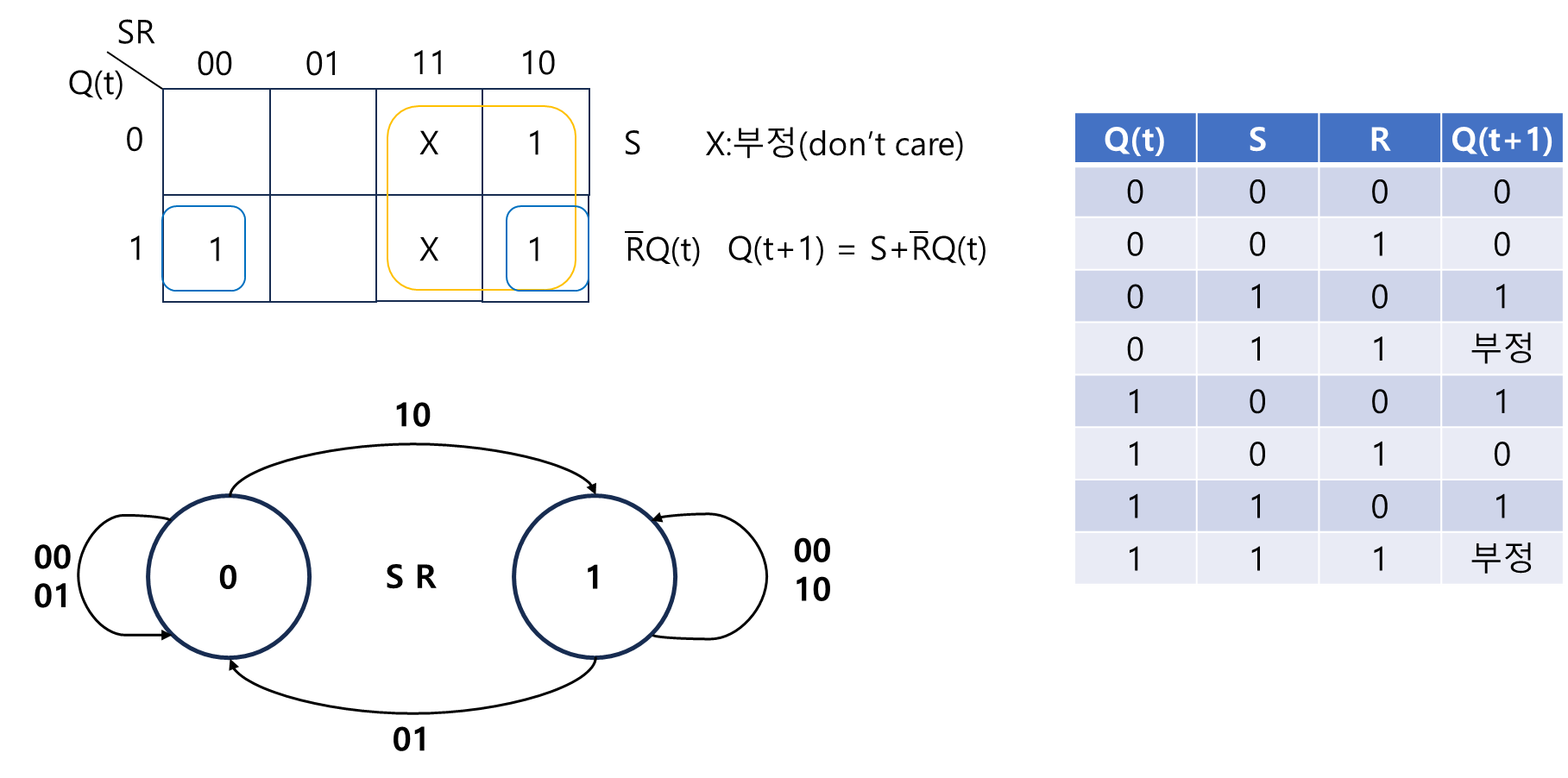

SR래치

SR래치의 진리표는 간단히 말하자면, Reset이 들어오면 무조건 0이 출력이 되며, Set 값이 들어오면 데이터가 출력이 된다고 생각하면 된다. (그것이 동작에 부정되는 값이라고 하더라도)

- 입력 S=0, R=0 일때 (NOR로 설명)

현재 출력 상태가 Q=0, Q'=1 인 경우

Q=0과 S=0이 G2(아래쪽 NOR)에 입력되면 Q' = 1이다.

Q'=1과 R=0이 G1(위쪽 NOR)에 입력되면, Q=0 이다.

따라서 S,R이 0인 입력되면 Q,Q'가 각각 0 ,1이 나오면서 현재 상태가 유지됨을 보인다. - 입력 S=0, R=1 일때 (NOR로 설명)

G1의 출력은 Q'에 상관없이 0 이된다. (Reset 신호가 들어왔기 때문에) 따라서 Q=0이 된다.

G2의 입력은 모두 0 이기 때문에 Q'1 =1 이 나온다.

따라서 Q=0, Q'=1의 값을 갖는다. - 입력 S=1, R=0 일때 (NOR로 설명)

G2의 출력은 입력의 상태에 관련 없이 0이 되기 때문에 (Reset 신호가 들어오기 때문) Q'=0이 된다.

G1은 모두 0이 입력되기 때문에 Q=1이 출력된다.

따라서 Q=1, Q'=0이 된다. - 입력 S=1, R=1 일때 (NOR로 설명)

Q와 Q'의 값이 보수가 유지 되지 않기 때문에 동작을 부정한다 해도 맞긴 하겠지만

S=1 R=1인 경우 특수한 경우를 통해 이해를 하는 것이 좋다.

입력이 S=1이고 R=1인 경우 Q와 Q'의 값이 0으로 출력된다. 이 상태로 다시 입력을 시킨다면 1이 출력이 나와야 처음 동작 규정에 맞겠지만, 그렇지 않기 때문에 위반됨을 알 수 있다.

2. SR플립플롭

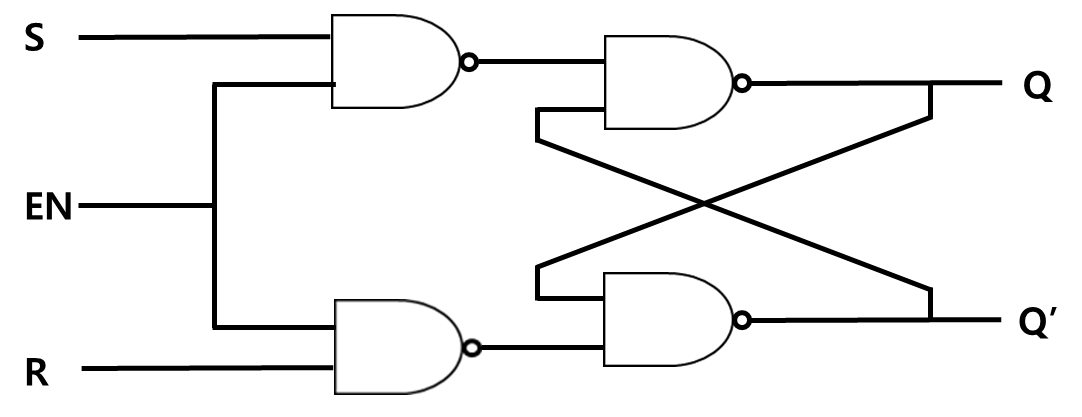

기본적인 SR래치는 S나 R 입력에 의해 바로 출력이 결정되는 비동기식 회로이다.

하지만 대부분 순서논리회로는 대부분 Clock Pulse 에 동기시켜 동작시킨다.

EN=0이면 G3, G4 NAND(가장 왼쪽, 위(G3), 아래(G4))의 출력이 모두 1이 되므로 Q와 Q'의 값이 변하지 않는다. 즉, EN=1인 경우에 동작하는 플립플롭이다.

- 입력 S=0, R=0 일때

G3와 G4의 출력 모두 1이 되기 때문에 출력은 변하지 않는다. (SR래치 S'1,R1'=1일때와 같다.) - S=0, R=1 일때

G3의 출력은 1이 되고, G4의 출력은 0 이 된다. 따라서 NAND 게이트 SR래치의 S'=1 R'=0인 경우와 같게 된다. - S=1, R=0 일때

G3의 출력은 0이 되고, G4의 출력은 1이 된다. 따라서 NANAD 게이트 SR래치의 S'=0 R'=1인 경우와 같다. - S=1, R=1 일때

G3와 G4의 출력이 모두 0이 된다. 따라서 NAND 게이트 SR래치의 S'=0 R'=0인 경우와 같다.(부정)

플립플롭은 기본적으로 Feedback이 존재하는 회로이며, EN=1인 상태에서는 모든 동작이 수행된다. 그러므로 동작시간보다도 EN의 지속시간이 길게 된다면 플립플롭은 여러 차례 동작이 수행 가능하고, 설계 예상과 다른 동작을 할 가능성이 있다.

이런 문제들을 해결하기 위해서 트리거를 사용하는 방법이 있다.

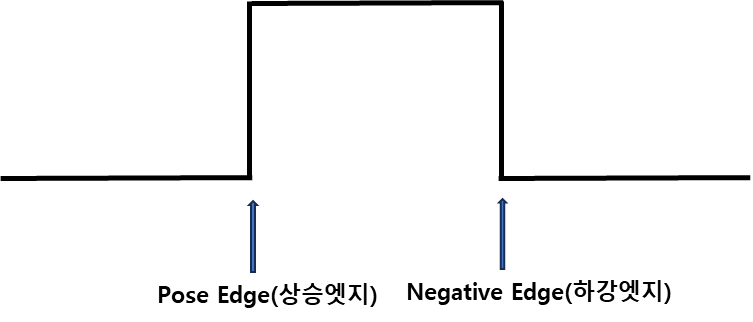

플립플롭은 입력신호의 순간적인 변화에 따라 출력을 결정할 수 있는데, 이런 변화를 트리거라고 하며 Level과 Edge로 구분하고 있다.

베릴로그를 배우면서 사용했던 트리거는 엣지 트리거로 (베릴로그 코드에서는 posedge나 negedge로 쓰인다.) 클록이 High에서 Low로 변하는 순간 혹은 Low에서 High로 변하는 순간에만 입력을 받아들이게 하는 방식이다.

레벨 트리거는 동작전압 혹은 EN 이 High 값으로 들어왔을때만 작동하게 하는 트리거를 말한다.

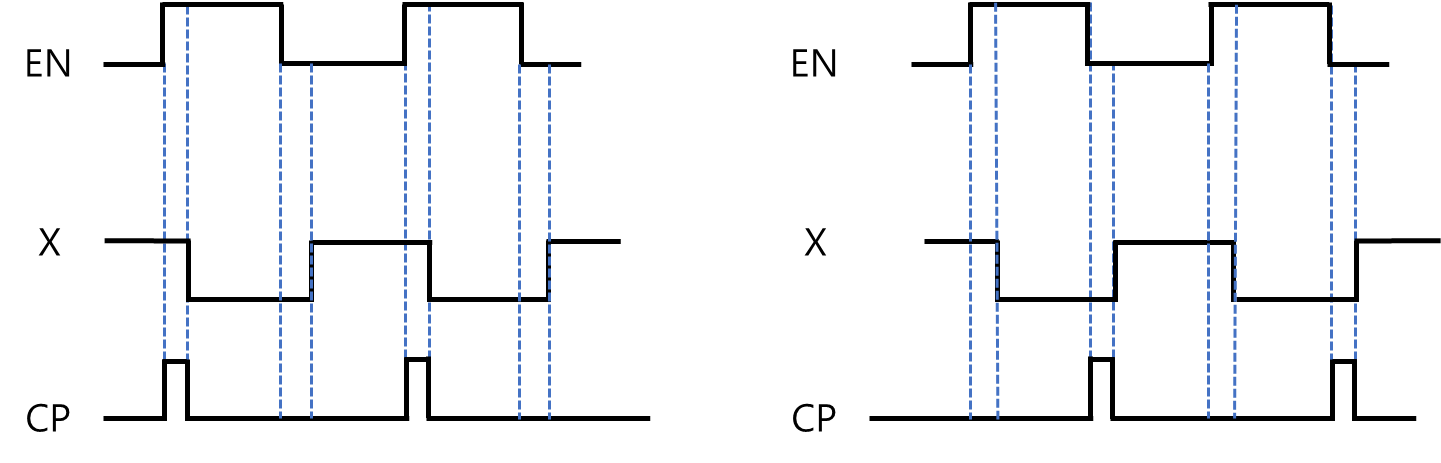

엣지 트리거는 상승엣지, 하강엣지로 나뉘며 윗 그림과 같다.

엣지 트리거 플립플롭은 입력값에 대해서 클록펄스의 에지 트리거에서만 동작을 출력하기 때문에 동기 입력(Synchronous input)이라고 한다.

3. D 플립플롭

4. JK플립플롭

5. T플립플롭