Kraklog

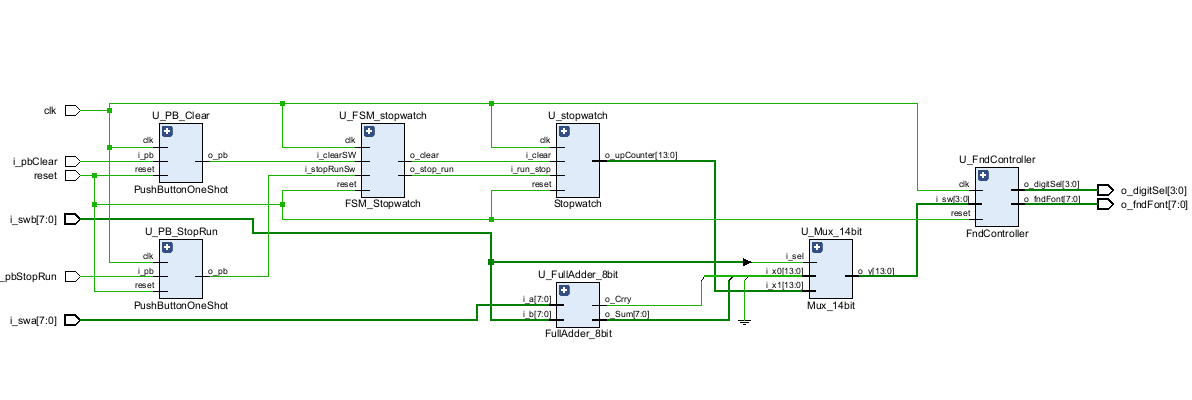

[Vivado] FSM (Stop Watch, 가산기) 본문

728x90

.

`timescale 1ns/1ps

module LED_FSM(

input clk,

input reset,

input i_ledSwitch,

output reg o_led

);

parameter S_OFF = 1'b0, S_ON = 1'b1 ;

reg state = S_OFF, nextState;

//state register

always @ (posedge clk, posedge reset) begin //next state part

if (reset) state <= S_OFF;

else state <= nextState;

end

// next state logic - event, change state

always @ (i_ledSwitch, state) begin

case (state)

S_OFF : begin

if(i_ledSwitch == 1'b1) nextState = S_ON;

else nextState = S_OFF;

end

S_ON : begin

if(i_ledSwitch == 1'b0) nextState = S_OFF;

else nextState = S_ON;

end

default : nextState = S_OFF;

endcase

end

/*// output logic - event, change state / moor

always @ (state) begin

case (state)

S_OFF : begin

o_led = 1'b0;

end

S_ON : begin

o_led = 1'b1;

end

default : o_led = 1'b0;

endcase

end

*/

// output logic - event, change state / meleay

always @ (state, i_ledSwitch) begin

case (state)

S_OFF : begin

if(i_ledSwitch == 1'b1) o_led = 1'b1;

else o_led = 1'b0;

end

S_ON : begin

if(i_ledSwitch == 1'b0) o_led = 1'b0;

else o_led = 1'b1;

end

default : o_led = 1'b0;

endcase

end

endmodule

`timescale 1ns / 1ps

module Calculator(

input clk,

input reset,

input [7:0] i_swa,

input [7:0] i_swb,

input i_pbStopRun,

input i_pbClear,

output [3:0] o_digitSel,

output [7:0] o_fndFont

);

wire [8:0] w_add;

wire [13:0] w_stopWatchValue, w_FNDSourceValue;

wire w_stopRunSW = i_swa[0], w_clearSW = i_swa[1], w_mode = i_swb[7];

wire w_stopRun, w_clear, w_pbStopRun, w_pbClear;

PushButtonOneShot U_PB_StopRun(

.clk(clk),

.reset(reset),

.i_pb(i_pbStopRun),

.o_pb(w_pbStopRun)

);

PushButtonOneShot U_PB_Clear(

.clk(clk),

.reset(reset),

.i_pb(i_pbClear),

.o_pb(w_pbClear)

);

FSM_Stopwatch U_FSM_stopwatch(

.clk(clk),

.reset(reset),

.i_stopRunSw(w_pbStopRun),

.i_clearSW(w_pbClear),

.o_stop_run(w_stopRun),

.o_clear(w_clear)

);

Stopwatch U_stopwatch(

.clk(clk),

.reset(reset),

.i_run_stop(w_stopRun),

.i_clear(w_clear),

.o_upCounter(w_stopWatchValue)

);

FullAdder_8bit U_FullAdder_8bit(

.i_a(i_swa),

.i_b(i_swb),

.o_Sum(w_add[7:0]),

.o_Crry(w_add[8])

);

Mux_14bit U_Mux_14bit(

.i_sel(w_mode),

.i_x0({{5{1'b0}}, w_add}),

.i_x1(w_stopWatchValue),

.o_y(w_FNDSourceValue)

);

FndController U_FndController(

.clk(clk),

.reset(reset),

.i_sw(w_FNDSourceValue),

.o_digitSel(o_digitSel),

.o_fndFont(o_fndFont)

);

endmodule728x90

'Study > VerilogHDL' 카테고리의 다른 글

| [Vivado] FSM (Stop Watch, 가산기) with button. (0) | 2023.08.04 |

|---|---|

| 레지스터와 카운터 (0) | 2023.08.04 |

| [Vivado] 2 bit Counter, 4x1 Mux, Clock Divider (0) | 2023.08.02 |

| [Vivado] 2x4 Decoder , 7-Segment (0) | 2023.08.02 |

| [Vivado] Adder (Half, 1bit Full, 4bit Full, 8bit Full) (0) | 2023.08.02 |