Kraklog

SoC sytem 본문

[SoC의 3가지 핵심 구성 요소]

1. CPU Core 2. Memory 3. 1개 이상의 Peripheral(주변기기)

[MCU와 FPGA 차이점]

공통점 :

Microcontroller Unit 과 Field Programmable Gate Array (각각 MCU,FPGA) 둘 다 디지털 시스템에서 사용되는 장치.

차이점 :

MCU

1. 고정된 하드웨어 : MCU는 일반적으로 하나의 칩 안에 프로세서 (core), 메모리, 주변장치 및 입출력 장치가 통합된 고정된 하드웨어를 가지고 있음.

2. 주로 작은 규모의 시스템에서 사용되며 주로 특정 애플리케이션을 위해 제작되기 때문에 유연성에 제한을 가질 수 있음.

3. MCU는 주로 고등언어를 사용하여 프로그래밍 되며, 이는 개발자에게 편리함을 줄 수 있지만, 하드웨어의 세부 사항은 추상화 되어 있어 개발자가 하드웨어를 직접 제어하기 어려울 수 있음.

4. MCU는 주로 저전력 소비가 중요한 배터리 구동장치, 센서 네크워크 등과 같은 분야에서 사용이 가능함.

FPGA

1. 프로그램 가능한 논리 블록을 가지고 있어 사용자가 원하는 디지털 논리 회로로 프로그래밍 가능함.

2. FPGA는 임의의 디지털 논리회로를 구현 할 수 있는 높은 수준의 유연성을 제공함.

(디지털 신호처리, 이미지처리, 특수한 컴퓨터 아키택쳐와 같은 분야에서 유용함)

3. FPGA는 특정 알고리즘이나 작업을 하드웨어로 가속화하여 높은 처리 성능을 얻을 수 있음. 이는 소프트웨어 구현만으로는 어려운 복잡한 계산을 하드웨어로 구현이 가능함을 의미

4. FPGA는 회로의 빠른 프로토타이핑 및 테스트를 가능케 하므로 새로운 디자인이나 알고리즘을 개발하는데 유용함.

5. FPGA는 일반적으로 높은 전력을 필요로 하며, MCU보다는 전력 소비가 높을 수 있음

[MCU / MPU]

-MCU : CPU의 기능을 하는 핵심 장치와 그 주변 장치들을 포함하고 있는 통합형 칩셋

-MPU : 주변에 RAM, ROM, I/O 등의 장치를 추가해주지 않으면 작ㄷ동을 하는 것이 불가능, 단지 CPU 그 자체만을 소형화 시켜 놓은 칩과 같음.

BusSize

한 번에 처리할 수 있는 bit 수

ex) 64bit, 32bit

Data band with

: 32bit * 4Ghz = 128Gbps /한주기 250ps

ALU (Arithmetic and Logical Unit, 산술 논리 장치)

: 덧셈 뻴셈 등 같은 두 숫자의 산술연산과 베타적 논리합 , 논리곱과 같은 논리연사을 계싼하는 디지털 회로.

산술 논리 장치는 컴퓨터 중앙처리장치의 기본 설계 블록

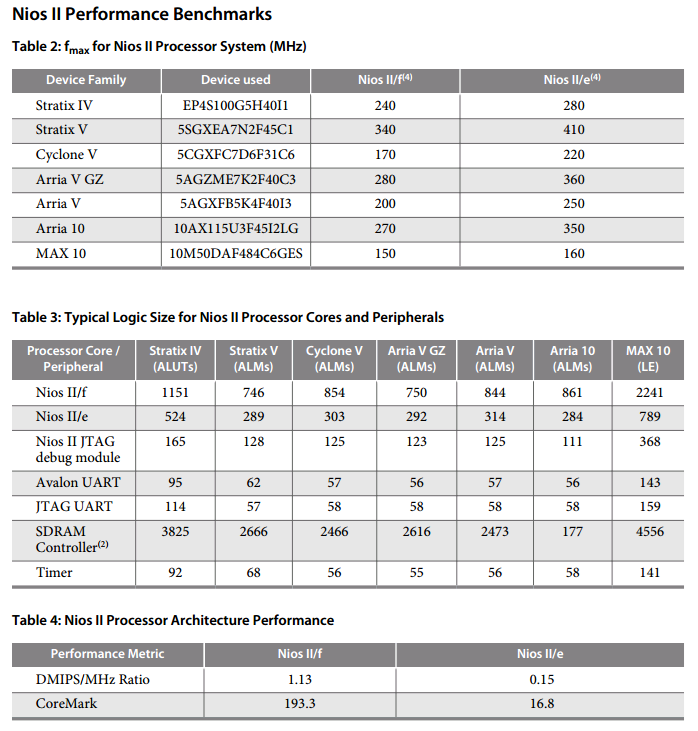

Nios II Processor

-Nios II Altera사의 FPGA기반 시스템에서 사용되는 32비트 RISC 아키텍처를 기반으로 한 프로세서.

NiosII 프로세서는 사용자가 애플리케이션 요구 사항에 맞게 프로세스를 최적화 할 수 있는 당야한 구성 옵션과 확장 가능성을 제공한다. 이는 사용자가 필요에 따라 주변 장치 및 기능을 추가하거나 제거하여 소프트웨어 및 하드웨어를 함께 디자인하고 개발할 수 있는 유연성을 갖는다는 말이다.

Nios II 는 소프트코어 마이크로 프로세서로 Programmable Logic Device (ex : ASIC , FPGA 등) 설계에 사용하기 위해 Intel이 설계 및 개발했다. 이를 통해서 사용자는 임베디드 시스템을 구축하기 위한 커스텀 하드웨어와 서프트웨어를 개발 할 수 있는 환경을 제공 받을 수 있다. 이러한 기능은 응용 프로그램의 특정 요구 사항에 따라 기능과 주변 장치를 사용자가 직접 정의할 수 있게 한다.

Nios II는 하버드 아키텍처를 사용한다. 또한 여러 Nios 코어를 하나의 FPGA에 통합할 수 있는 대칭형 다중 처리방식 (SMP)를 지원하기 떄문에 병렬처리 작업에 유용하다.

[프로그래머블 로직, Programmable Logic]

특정 기능이나 작업을 수행하기 위해 디지털 논리 회로를 설계하고 재구성하는 기능을 말한다. VHDL이나 Verilog와 같은 HDL언어를 사용하며 Programmable Logic 구현을 위해 ASIC, FPGA 그리고 CPLD와 같은 Programmable Logic Device가 주로 사용된다.

[소프트 코어 마이크로 프로세서, Soft Core Micro Processor]

소프트 코어 마이크로 프로세서는 주로 FPGA나 ASIC에 소프트웨어로 구현되며, 하드웨어 수정 없이 소프트웨어 업데이트로 기능을 변경 할 수 있는 ㅂ마이크로 프로세서이다. 주변 장치와 기능을 통합하여 특정 응용 분야에 맞게 프로그램 가능한 장치에 유연하게 적용되며, 빠른 프로토타이핑과 수정이 가능한 특성을 갖추고 있음

주로 임베디드 시스템 및 디지털 신호 처리 분야에 활용.

[하버드 아키텍처, Harvard Architecture]

명령어와 데이터를 별도의 메모리에 저장하는 구조를 가지고 있으며, 명령을 메모리로부터 읽는 것과 데이터를 메모리로 부터 읽는 것을 동시에 수행할 수 있다.

폰 노이만 아키텍처는 명령어와 데이터가 같은 메모리에 저장되는 반면, 하버드 아키텍처는 명령어와 데이터가 별도의 메모리에 저장되어 독립적인 메모리 버스를 사용하게 된다. 이로 인해 하버드 아키텍처는 명령와 데이터의 병렬 처리를 가능하게 하며 성능향상에 기여할 수 있지만, 처리 속도를 높이려면 더 많은 전력소모가 단점이다.

Nios II 는 크게 2가지 버전이 있고(더 나눈다면 Fast, Economy, Standard), 적은 용량을 차지하고 프로세서 내부 구조가 간단한 nios II economy core가 있고 fast core 가 있다.

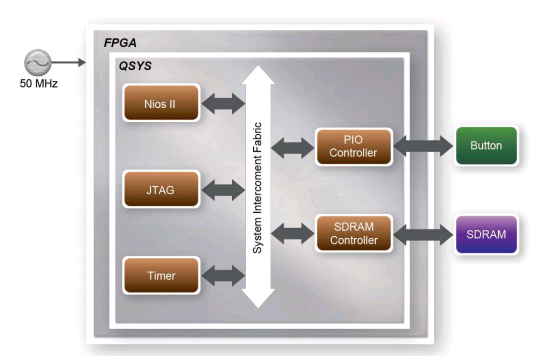

Nios II 프로세서를 사용하게 되면 기존의 MCU내부의 주요 장치들을 쉽게 추가할 수 있고 또한 FPGA로직을 사용해서 사용자가 만든 주변장치도 추가할 수 있습니다. 즉 타이머가 필요하면 원하는 만큼 추가할 수 있으며 또한 UART가 여러개 필요하면 추가하고 연결해 주면 됩니다.

[Bus]

Avalon BUS

-CPU, Memory는 instruction, bus, data bus 로 연결 되어있고, 나머지는 data bus로 연결되어 있다.

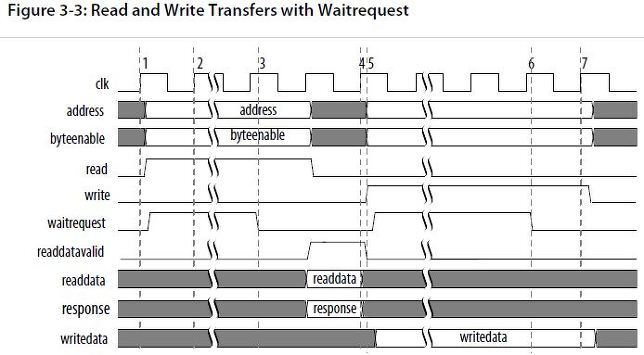

-BUS에는 Address (32bit) read, write, data in(32bit), data out(32bit) 의 구성요소가 필요하다.

1. address, byteenable, and read are asserted after the rising edge of clk.

The slave asserts waitrequest, stalling the transfer.

2. waitrequest is sampled. Because waitrequest is asserted, the cycle becomes a wait-state.

Address,read, write, and byteenable remain constant.

3. The slave deasserts waitrequest after the rising edge of clk.

4. readdata, response and deasserted waitrequest are sampled, completing the transfer.

5. address, writedata, byteenable, and write signals are asserted after the rising edge of clk.

The slave asserts waitrequest stalling the transfer.

6. The slave deasserts waitrequest after the rising edge of clk.

7. The slave captures write data ending the transfer.

[Avalon-MM인터페이스]

Avalon-MM은 주로 메모리 맵 형식의 데이터 전송에 사용됩니다. 마이크로프로세서나 다른 주변 장치와의 통신을 위한 표준 메모리 맵 인터페이스를 제공하며, 읽기와 쓰기 사이클을 포함하는 데이터 전송을 지원합니다.

[Avalon-ST인터페이스]

Avalon-ST는 연속적인 데이터 스트림을 처리하는 데 사용됩니다. 주로 디지털 신호 처리 (DSP)나 다른 데이터 스트리밍 응용 분야에서 활용되며, 실시간 데이터의 효율적인 전송을 위한 인터페이스를 제공합니다.

'[Harman] 하만 반도체 설계 > NiosII' 카테고리의 다른 글

| Avalon PWM, PWM Interrupt (0) | 2023.09.08 |

|---|---|

| Avalon BUS + reg 설계 (0) | 2023.08.28 |

| PWM / CRC (0) | 2023.08.28 |

| Nios Processor (0) | 2023.07.28 |

| Day25. Simple UART TX & RX (0) | 2023.07.28 |