Kraklog

[하만] DAY2.디지털 논리게이트 설계 (NAND, NOR 작성) 본문

[하만] DAY2.디지털 논리게이트 설계 (NAND, NOR 작성)

Krakens 2023. 7. 6. 01:36사용프로그램 : Cadence Virtuoso

Design Rule : Gpdk090

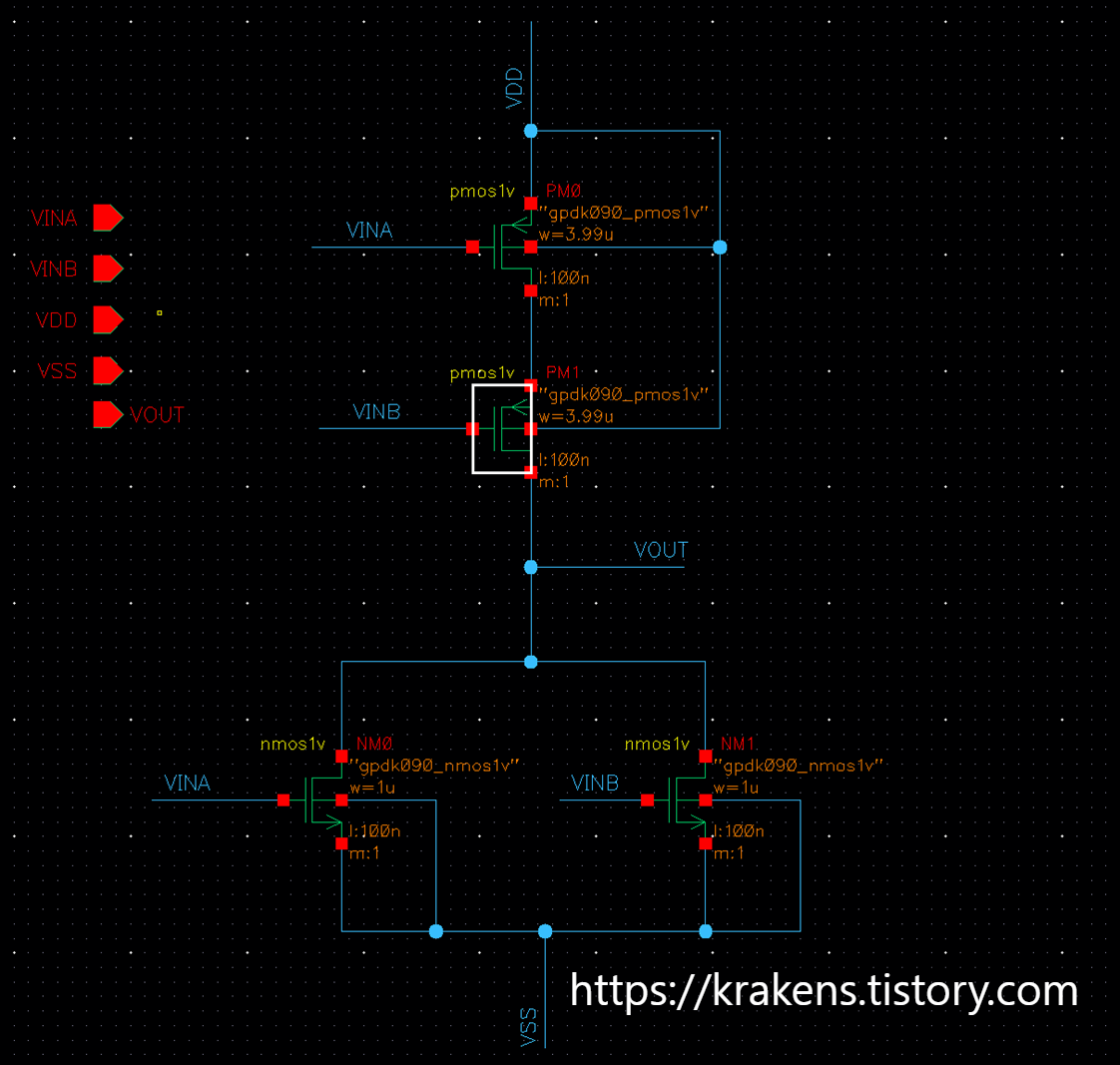

2NAND

1. 이론

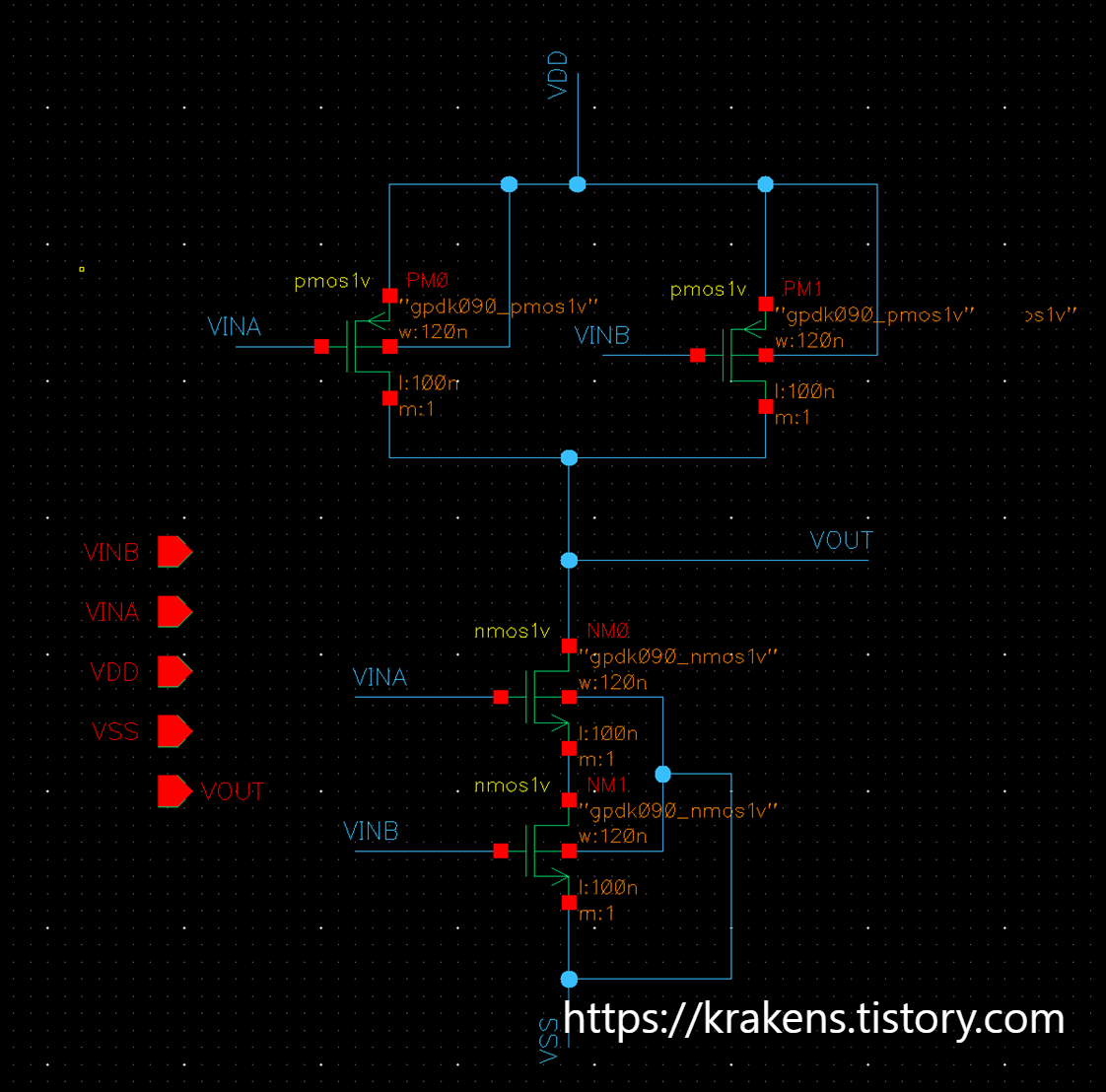

- Schematic Diagram

Logic 과 진리표를 구성은 다음과 같다.

NAND 게이트는 AND + NOT으로 생각 할 수 있다. (심볼과 진리표 참조)

AND + NOT으로 논리회로를 구성해도 똑같이 작동하기에 반도체 설계에서도 큰 문제는 없지만,

정해진 웨이퍼 규격안에 최대한 많이, 공정비를 낮춰서 (들어가는 소자를 줄여서) 효율을 올려야하는 반도체 공정에서

AND + NOT 구조는 이점이 없다고 생각된다.

NAND 게이트의 트랜지스터 수 : pMOS 2개, nMOS 2개

AND + NOT 게이트 TR 수 : pMOS 2개 nMOS 2개 (AND게이트) + pMOS 1개 nMOS 1개 (NOT게이트)

NAND는 입력 B가 0에서 1로 변할 때 출력 값이 변하기 때문에 이걸 기반으로 시뮬레이션을 통해 pMOS의 길이를 변환해주면 된다.

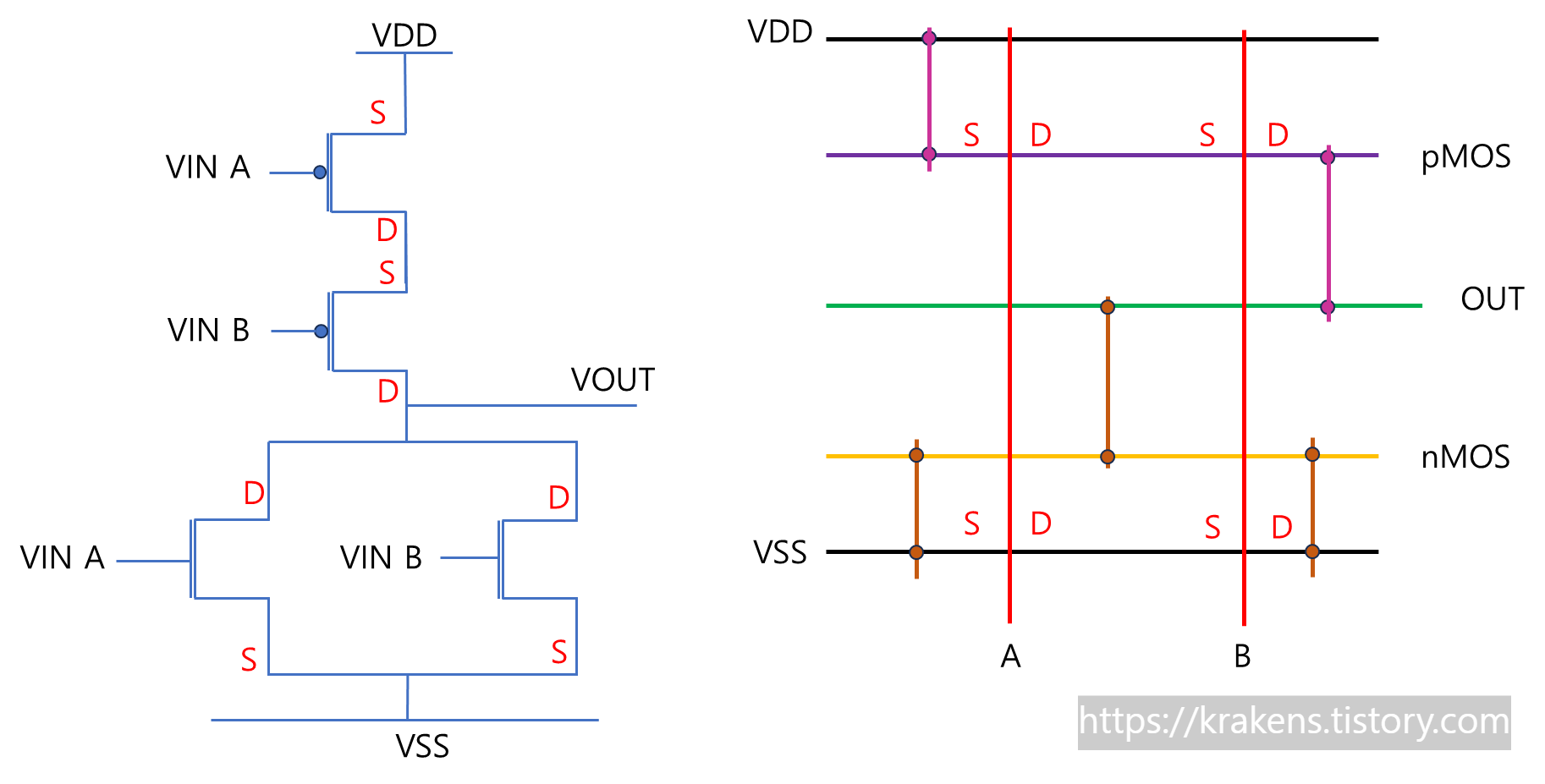

Stick Diagram을 그리면 다음과 같이 그릴 수 있는데 (꼭 저렇게만 그릴 수 있는게 아님)

Stick Diagram을 그리는기 위해 Path를 정해야하는데

막히지 않고 한 번에 출력으로 가는 경로를 찾아줘야한다. (화살표 방향으로 정했음)

그런 후 Stick Diagram을 그려줬는데 Drain과 Source의 구성은 바꿔줄 수 있겠지만

출력을 하나로 줄여주는게 처리 속도에서 이득이 있기 때문에 저렇게 구성을 해줬다.

2. Design

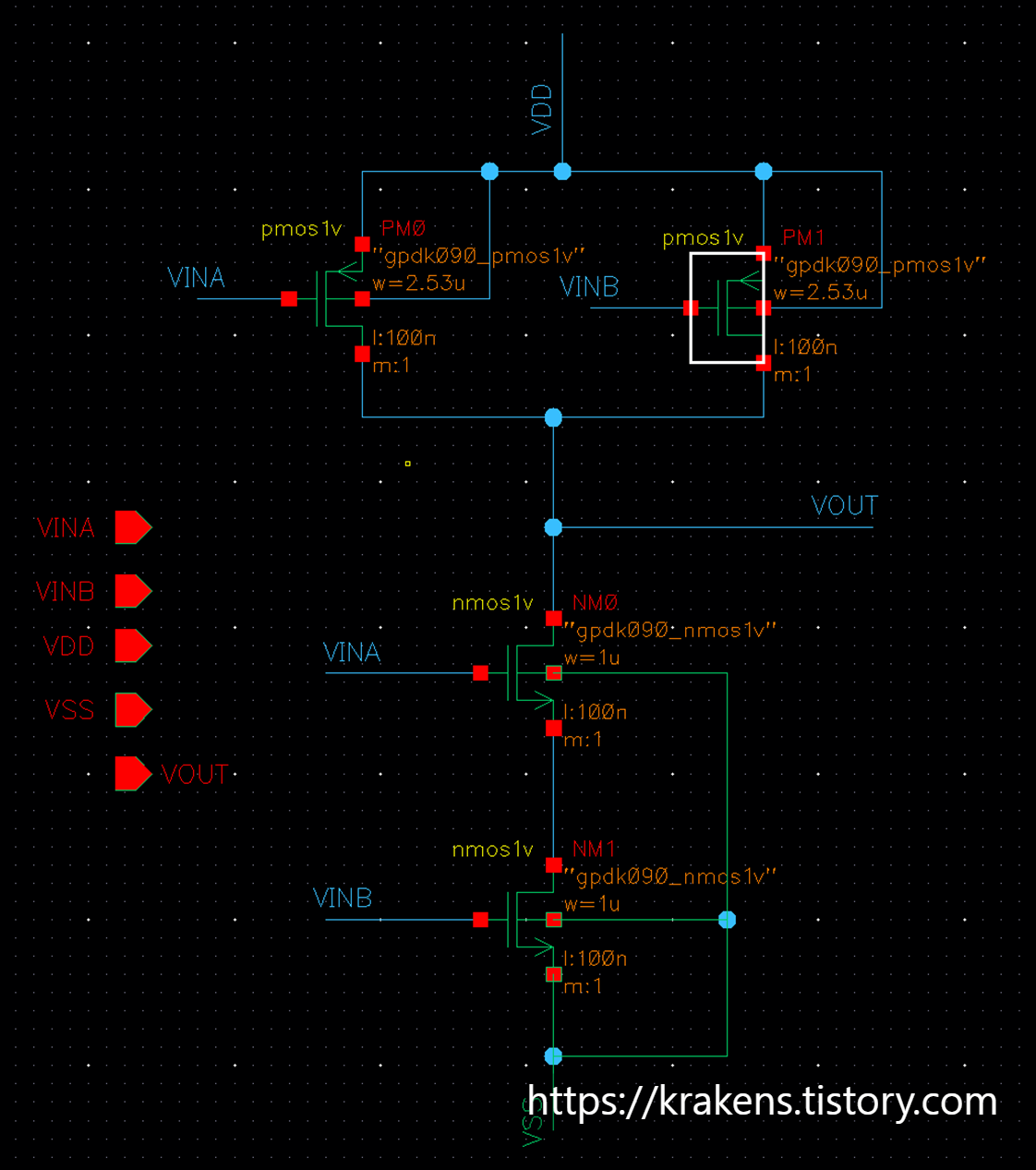

- Schematic

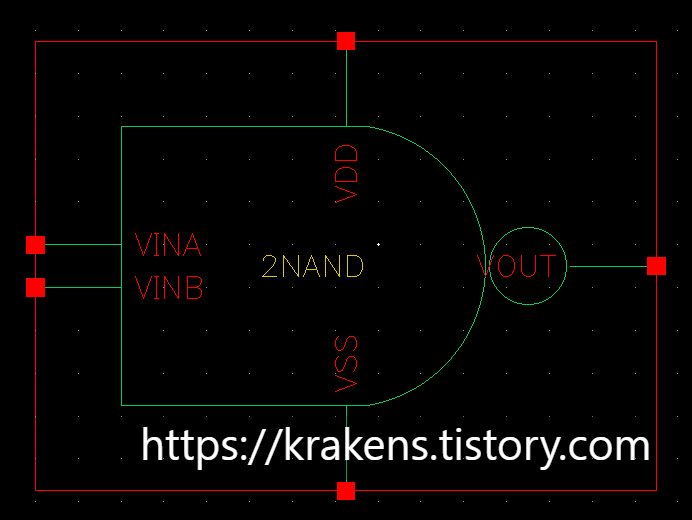

- Symbol

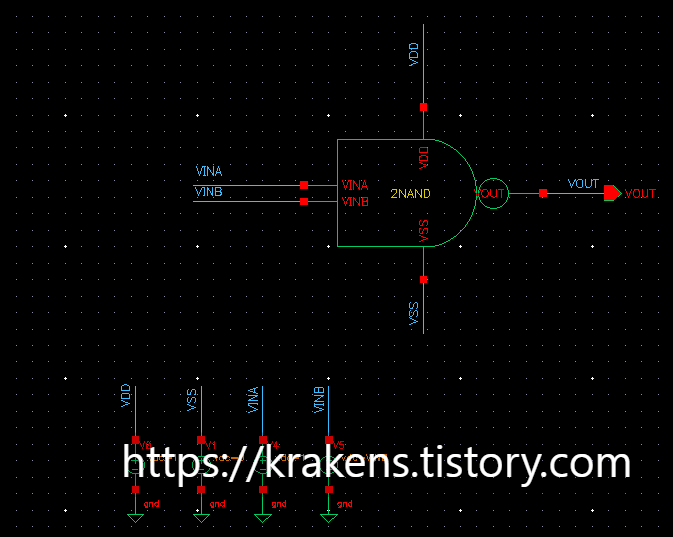

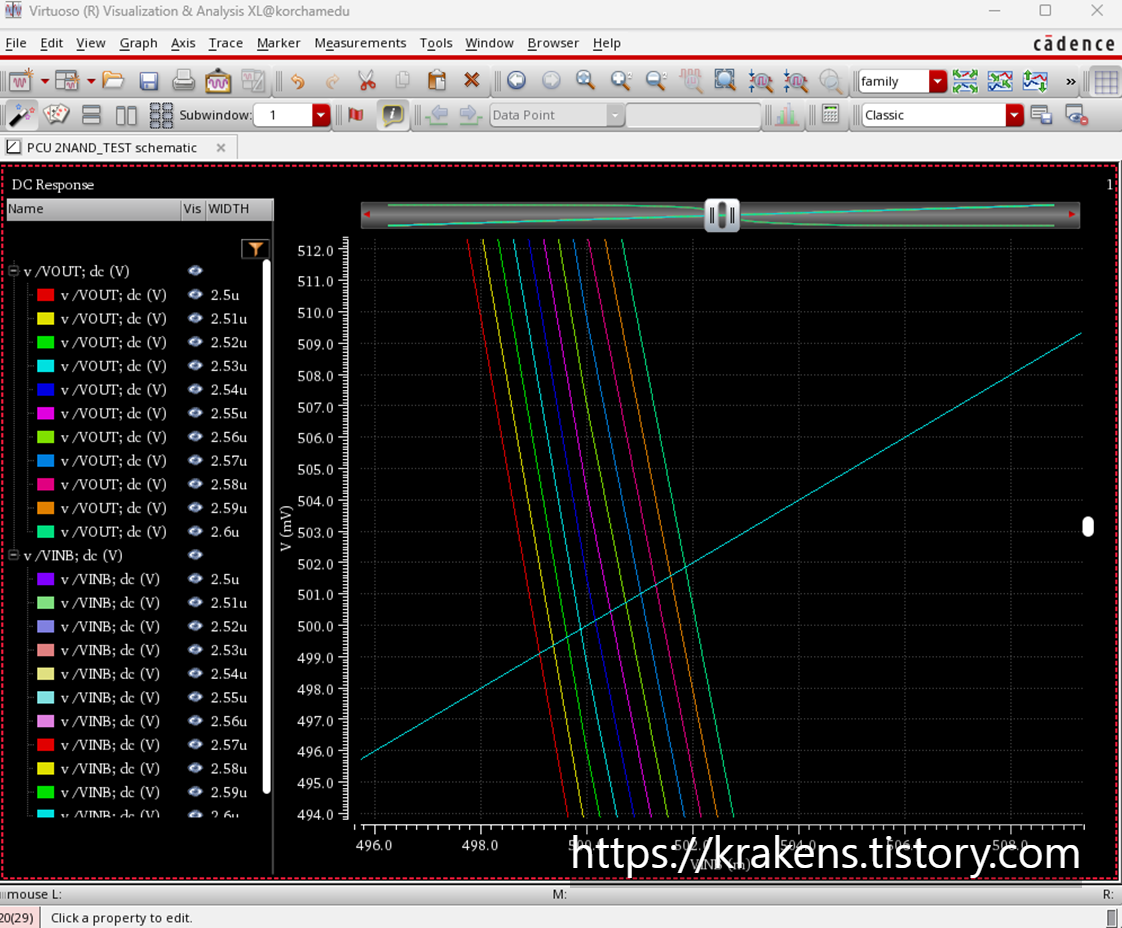

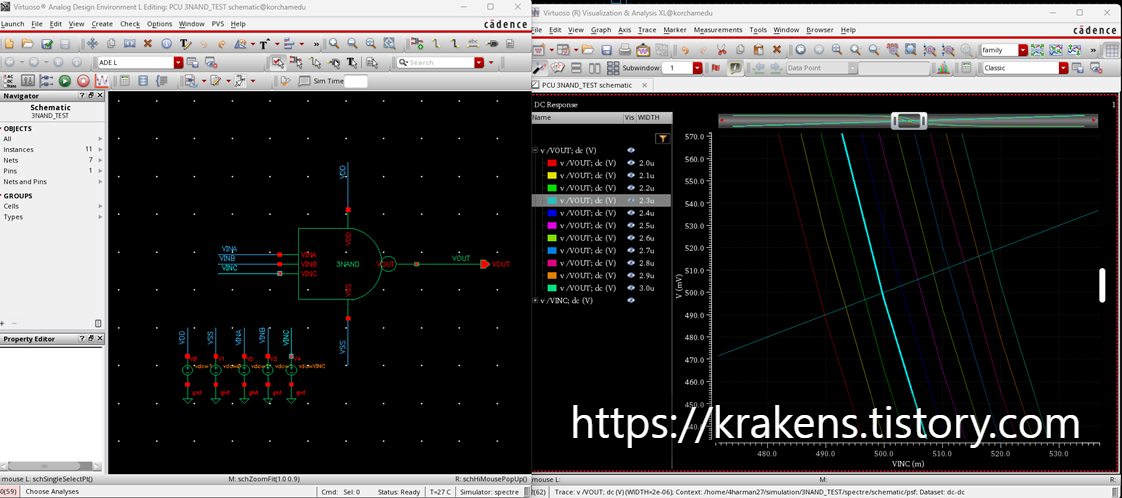

3. Simulation

시뮬레이션 결과 2NAND pMOS의 값을 2.53u로 두고 설계를 마무리 했다.

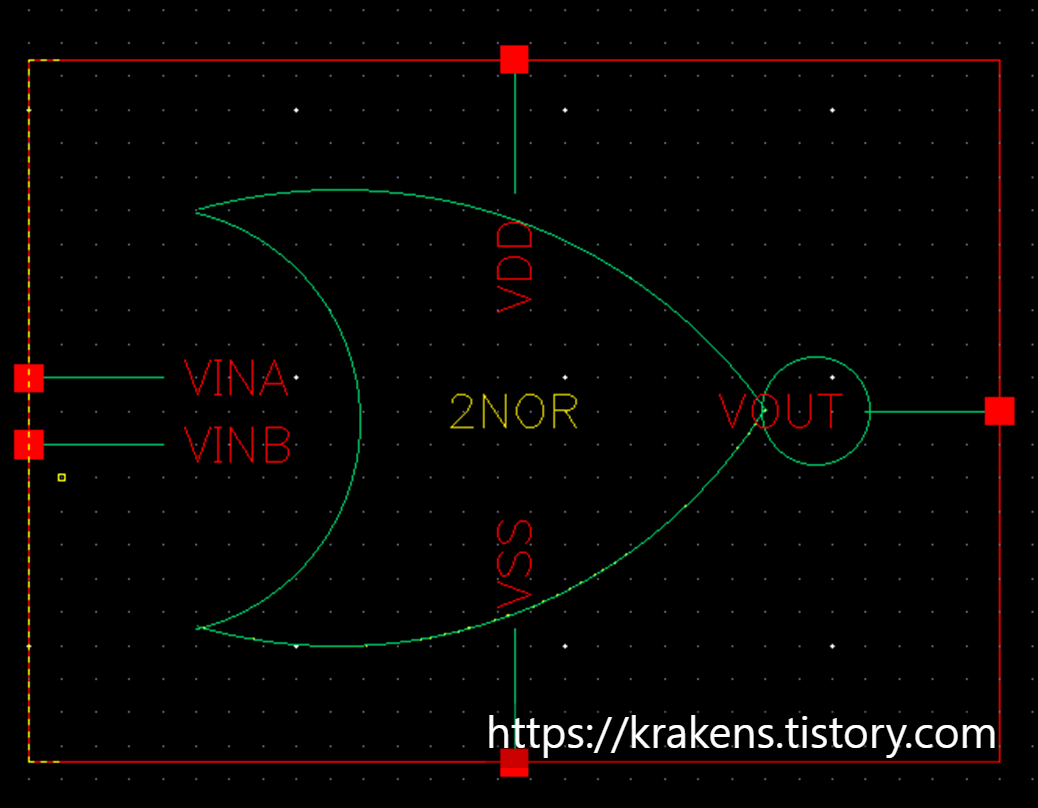

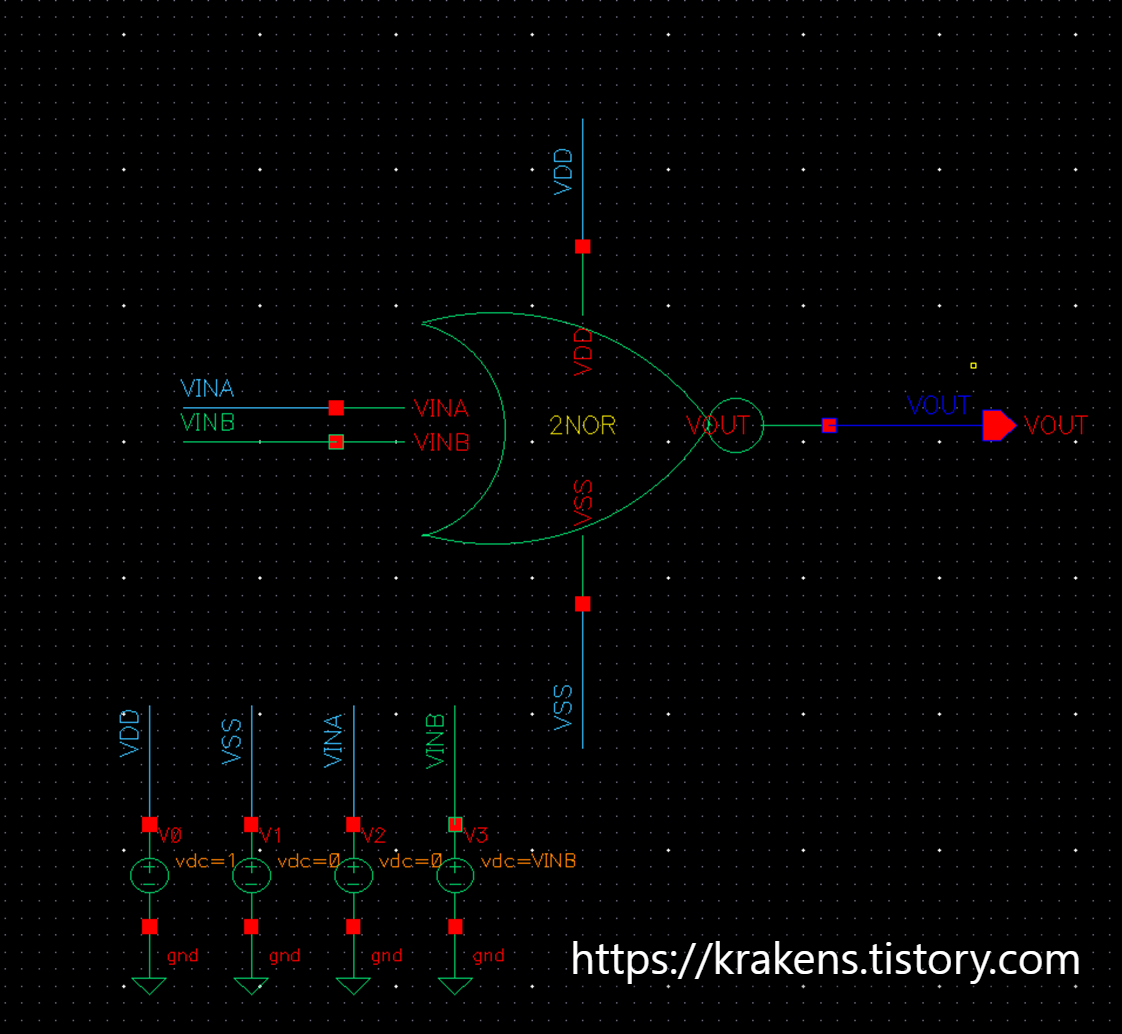

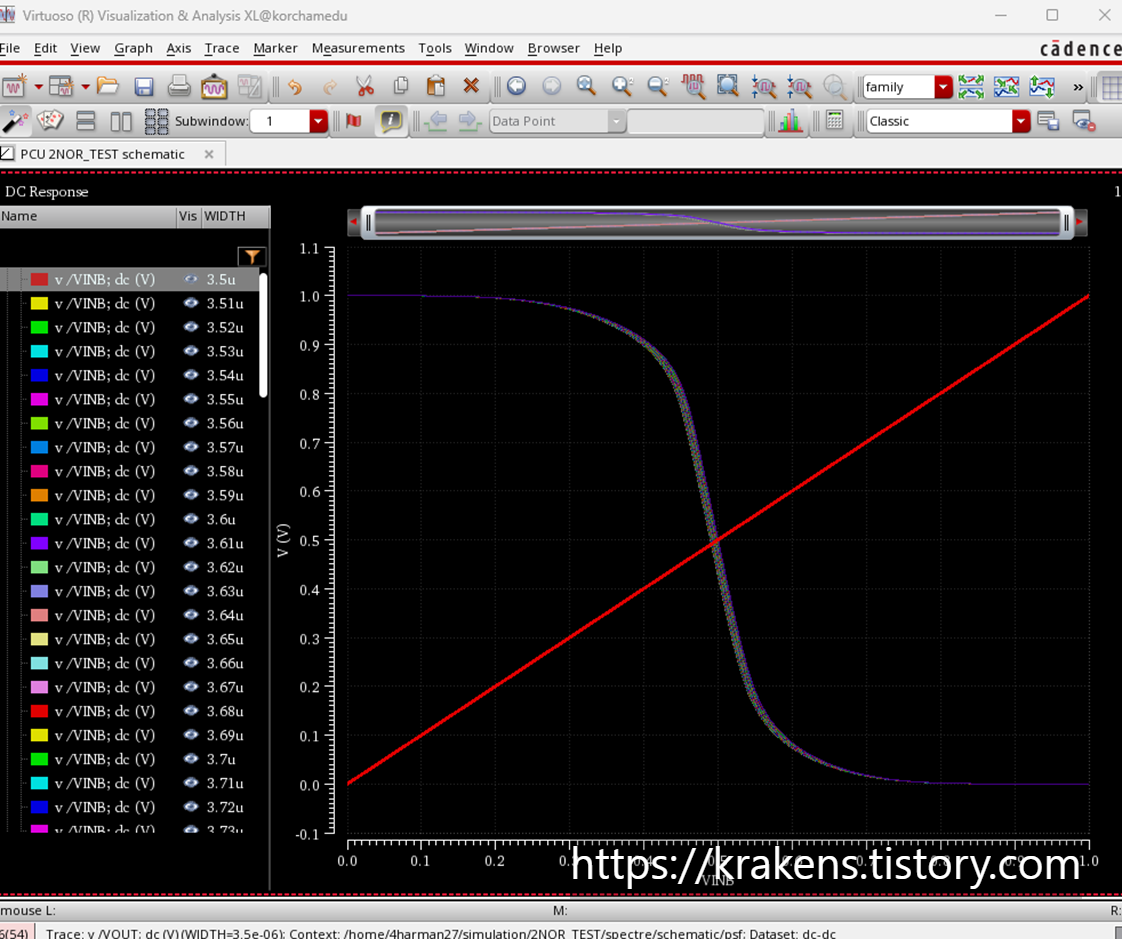

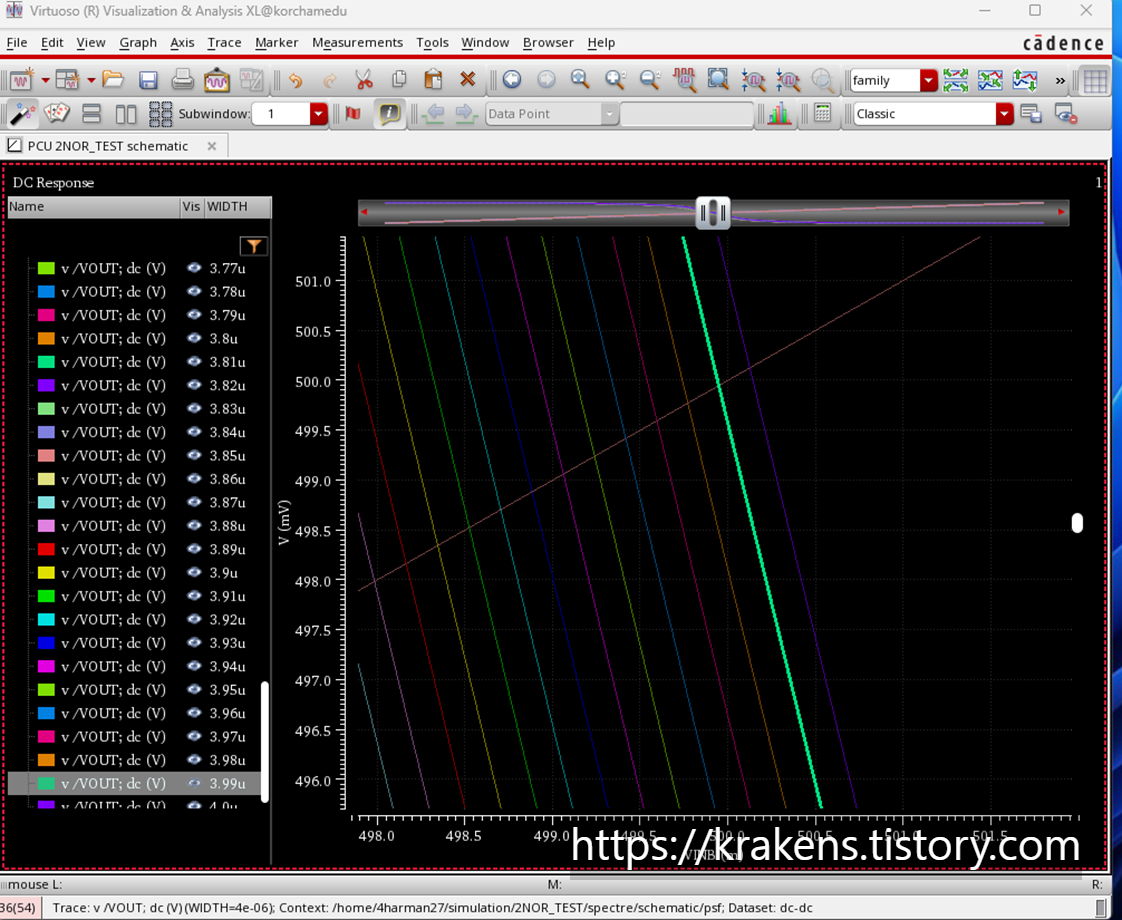

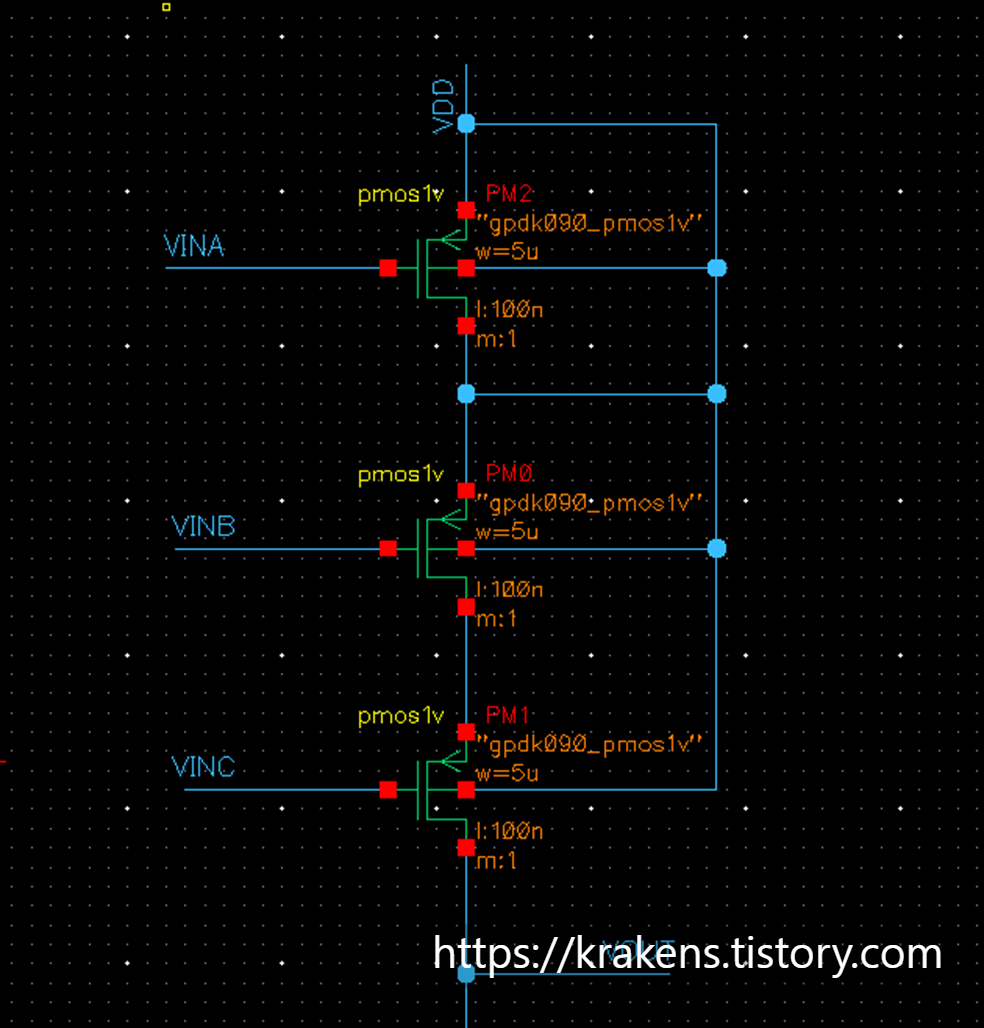

2NOR

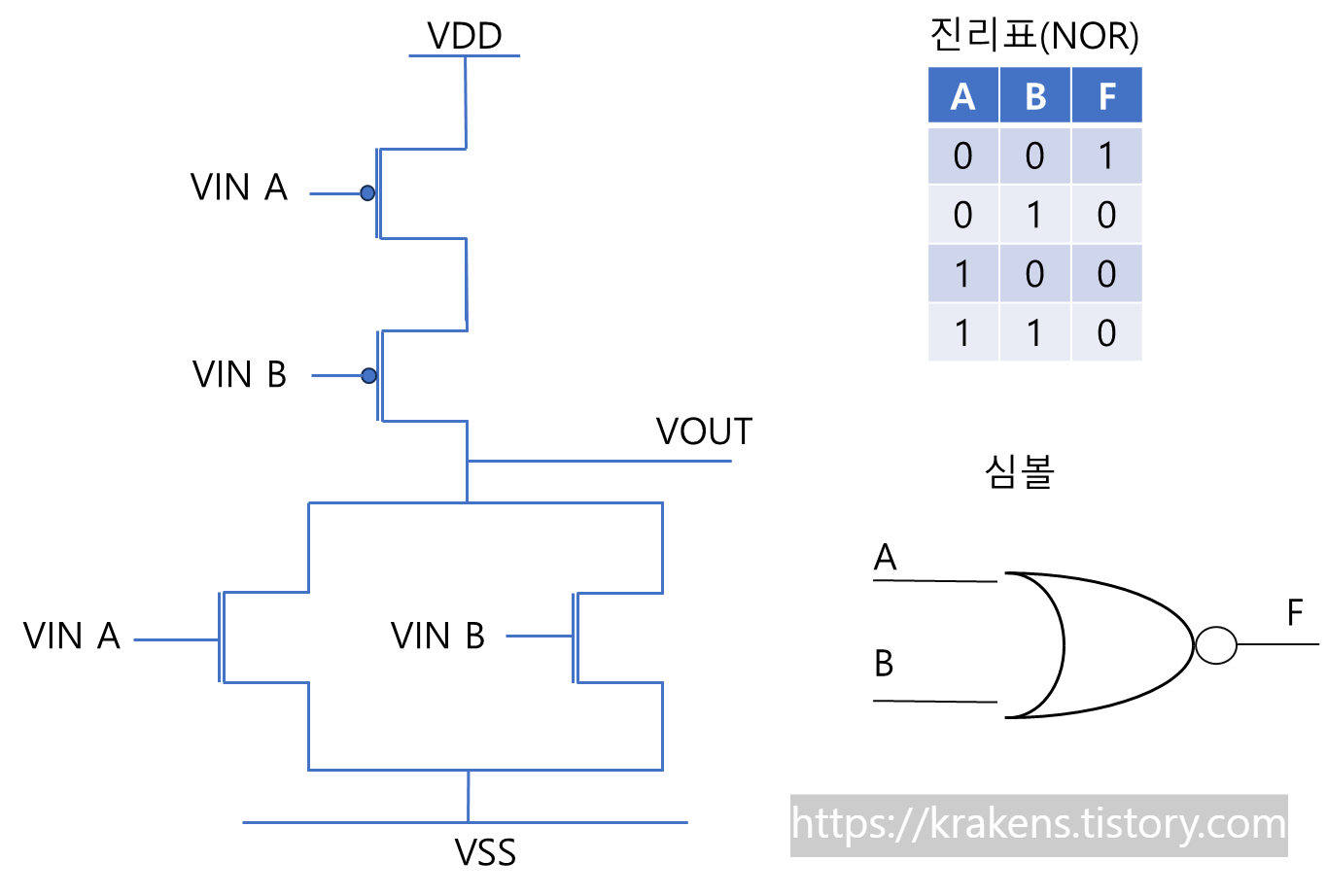

1. 이론

NAND와 유사하지만 B가 1에서 0으로 바뀌었을때 (0에서 1로 바뀌었을때) 출력이 바뀌므로, 이걸 기준으로 시뮬레이션을 할 예정이다.

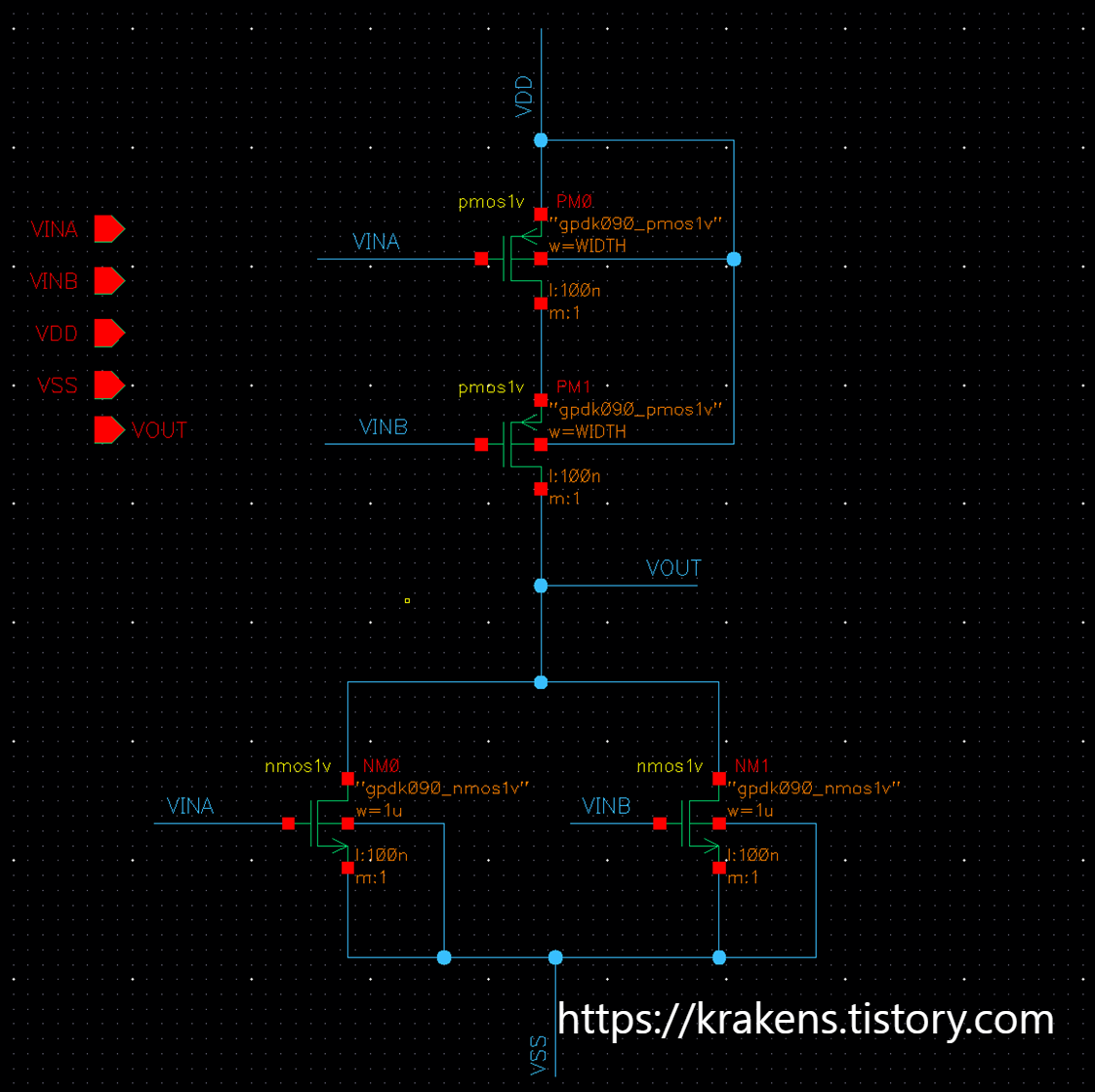

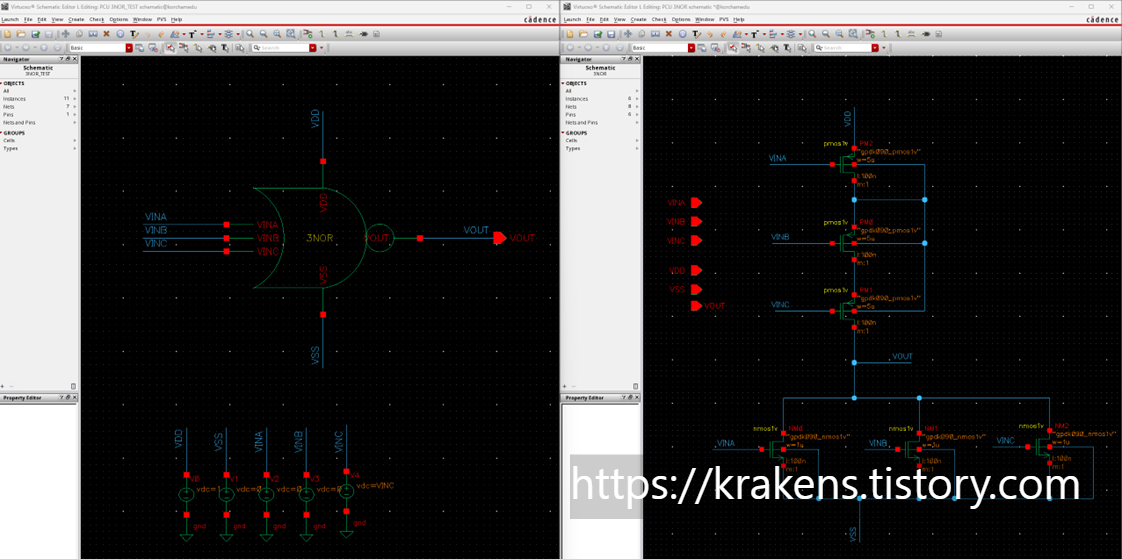

2. Design

- Schematic Diagram

- Symbol

- Test Schematic

3. Simulation

3NAND, 3NOR

'[Harman] 하만 반도체 설계 > Full Custom One Chip' 카테고리의 다른 글

| [하만]DAY4. 21MUX LOGIC 작성 (0) | 2023.07.08 |

|---|---|

| [하만] DAY3. LAYOUT 디자인 (0) | 2023.07.08 |

| [하만] DAY1.NOT(Inverter) 설계 (0) | 2023.07.06 |

| [하만] Cadence Virtuoso 초기 사용법 (0) | 2023.07.06 |

| [하만] DAY1.5 - 반도체 이론 용어 (0) | 2023.07.06 |