Kraklog

[Verilog_LAB1] Part4 본문

728x90

프로그램 : Quaturs Prime lite edition 18.1

사용문법 : Verilog 2001

보드 : DE1-SOC

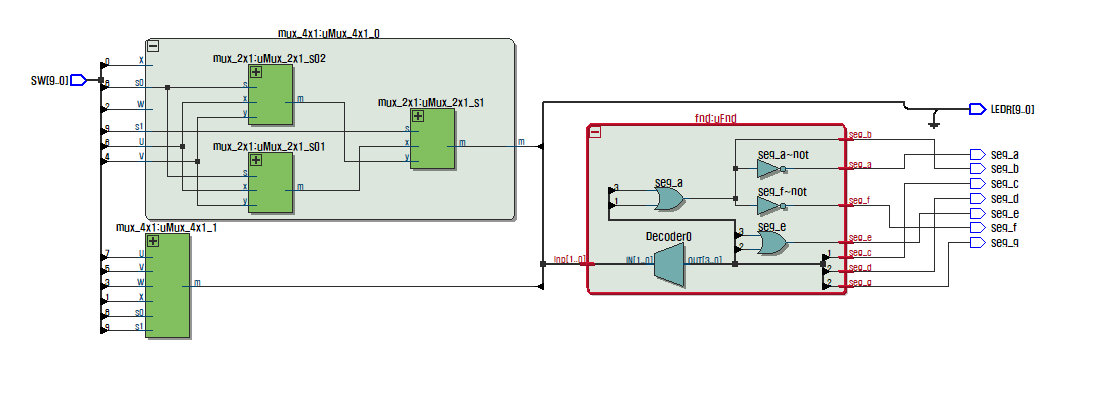

part4의 목표는 7-Segment 제어이다.

c1c0의 값에 따라서 segment에 글씨를 표현하는 것인데, DE1-SoC 보드이기 때문에 기본적으로 dE1을 표현하고, 추가적인 사항으로 S의 값도 추가하였다.

`define BUS_SIZE 2

`define SL_SIZE 10

//`define USE_GNE

module part4(SW,LEDR,seg_a,seg_b,seg_c,seg_d,seg_e,seg_f,seg_g);

input [`SL_SIZE-1:0] SW;

output [`SL_SIZE-1:0] LEDR;

output seg_a;

output seg_b;

output seg_c;

output seg_d;

output seg_e;

output seg_f;

output seg_g;

wire [`BUS_SIZE-1:0] U;

wire [`BUS_SIZE-1:0] V;

wire [`BUS_SIZE-1:0] W;

wire [`BUS_SIZE-1:0] X;

wire [`BUS_SIZE-1:0] m;

wire s1,s0;

assign s1 = SW[9];

assign s0 = SW[8];

assign U=SW[7:6];

assign V=SW[5:4];

assign W=SW[3:2];

assign X=SW[1:0];

assign LEDR [1:0] = m;

assign LEDR [`SL_SIZE-1:2] = 0;

`ifdef USE_GNE

genvar i;

generate

for (i=0; i<2; i=i+1)begin : MUX_2x1

mux_4x1 uMux_4x1(

.U(U[i]),

.V(V[i]),

.W(W[i]),

.X(X[i]),

.s0(s0),

.s1(s1),

.m(m[i])

);

end

endgenerate

`else

mux_4x1 uMux_4x1_0(

.U(U[0]),

.V(V[0]),

.W(W[0]),

.X(X[0]),

.m(m[0]),

.s0(s0),

.s1(s1)

);

mux_4x1 uMux_4x1_1(

.U(U[1]),

.V(V[1]),

.W(W[1]),

.X(X[1]),

.m(m[1]),

.s0(s0),

.s1(s1)

);

`endif

/* always @ (*)

if (!s1)

LEDR = m1;

else

LEDR = m2;*/

fnd uFnd(

.inp (m ),

.seg_a(seg_a),

.seg_b(seg_b),

.seg_c(seg_c),

.seg_d(seg_d),

.seg_e(seg_e),

.seg_f(seg_f),

.seg_g(seg_g)

);

endmodule#2001 버전이 아닌 올드타입을 따랐는데, 지시서에 적혀있어서 이용했음

mux4x4는 이전 발행글에서나온 mux를 이용하였다. (2023.12.18 - [[Harman] 하만 반도체 설계/CPU설계] - [Verilog_LAB1] Part3)

module fnd (

input [1:0] inp ,

output reg seg_a ,

output reg seg_b ,

output reg seg_c ,

output reg seg_d ,

output reg seg_e ,

output reg seg_f ,

output reg seg_g

);

always @ (*) begin

case (inp)

2'b00 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g } = ~7'b011_1101;

2'b01 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g } = ~7'b100_1111;

2'b10 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g } = ~7'b011_0000;

2'b11 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g } = ~7'b101_1011;

default : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g } = ~7'b111_1110;

endcase

end

endmodulefnd 모듈

728x90

'[Harman] 하만 반도체 설계 > CPU설계' 카테고리의 다른 글

| [Verilog_LAB2] Part1 (0) | 2023.12.19 |

|---|---|

| [Verilog_LAB1] Part5 (0) | 2023.12.18 |

| [Verilog_LAB1] Part3 (1) | 2023.12.18 |

| [Verilog_LAB1] Part2 (1) | 2023.12.18 |

| [Verilog_LAB1] Part1 (0) | 2023.12.18 |