Kraklog

Day33. 회로이론(옴의 법칙) 본문

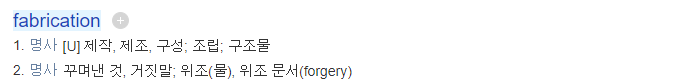

반도체 공정 용어 :

Fabrication : 제작, 제조로 쓰이며 FAB in 이라는 축약어로 사용된다.

QC : Quality Control - 품질관리

QA : Quality Assurance - 품질 보증

Yiedl - 수율

Foundary - fab, Semiconductor + Fabrication plant

Fab less - Design House - Front End

Dip type - Dunal in line Package - 일반적으로 사용했던 저항에서 주로 볼 수 있음

SMD type - Surface mounted device - PCB 납 마스크에 올려서 납땜해서 쓰이는 타입.

(진짜 시작)

- 전류(Current)

전하의 이동 또는 흐름, 단위시간 1초 동안 이동한 전하량

단위 : [A]

Q = It [C]

전하의 국제단위는 쿨롱이며, 단위기호는 C이다.[1] 1 쿨롱은 매우 큰 단위이며, 약 6.25×1018개의 전자나 양성자들의 전하량이다. 반대로, 전자 또는 양성자 한 개의 전하량은 1.6021773349 ×10-19 쿨롱이며,[2] 이를 기본 전하라고 부른다. *위키피디아 - 전위(Potential) : 전기적 위치에너지

전압(Voltage, [V]) : 1[V] 는 1[C]의 전하를 1[J]의 에너지로 이동시킬 수 있는 전위 - Source ⇔Load

Voltage Source (전압원)

ideal 전압원의 등가내부 저항은 0Ω

Current Source (전류원)

ideal 전류원의 등가 내부 저항은 ∞Ω - 저항에 흐르는 전류와 저항 양단의 전압 계산하시오

-전류 : 일반적으로 부하에서 흐른다.

R2 저항의 좌측단은 2V 전압이 걸리고, R2의 우측단은 1V의 전압이 걸린다.

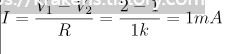

회로 해석 : 전압 Source는 전압 고정이기 때문에 전류는 주변 단자에서 결정해준다.

위 회로에선 R2 저항이 전류를 결정해준다.

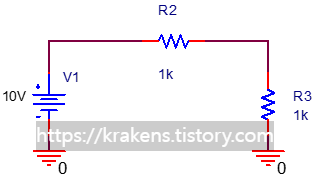

- 아래 회로에 대해 답하시오.

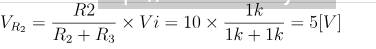

회로 해석 : 직렬회로 (Serial Circuit) 는 입력 전압을 저항들이 나눠 갖는다.

1. 저항이 클수록 전압이 높다.

2. R1 과 R2가 같다면, V= 0.5 Vi 가 적용된다.

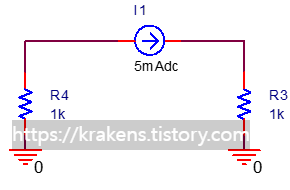

회로 해석 : 전류원은 전류가 고정이기 때문에 전압은 주변회로에서 결정이 된다.

R4의 윗부분을 Va라고 한다면, Va - GND = Va-0 이다.

옴의법칙을 이용해 R4에 걸리는 전압을 계산하면 Va= R4 * 0.5mA = 5V 임을 계산 가능하다.

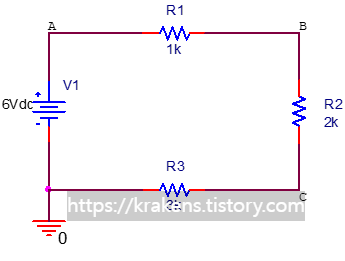

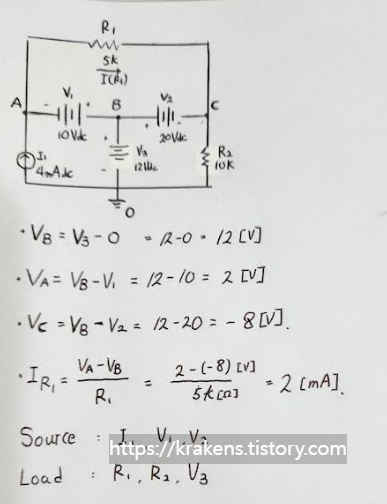

- 아래 회로에서 각 노드의 전압을 계산하시오.

회로 해석 : GND를 기준으로 잡고, 전류의 방향을 구해주었다. (전압원의 양 방향이 R1에 맞닿아 있기 때문에, 전류의 방향은 R1 to R3로 정했다. - 반드시 이렇게 정하지 않아도 결과값은 같다, )

해석 방법은 전압분배를 이용해서 구하는 방법과, 전류를 구해서 전압을 구하는 방법이 있겠다.

전체 전류는 전체 저항을 전압으로 나눠준 값인데, 1mA가 된다.

이 전류를 통해 각 저항에 걸리는 전압을 구하면, VR1은 1V, VR2는 2V VR3는 3V가 된다. 전류의 방향에 따라서 노드의 전위차를 계산해서 적어주면 Va는 6, Vb는 5 Vc는 3으로 그 값을 구할 수 있다.

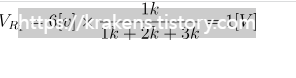

다음은 전압 분배를 이용한 방법인데, 직렬회로는 저항들이 입력전압을 나눠 갖는다.

Vr1에 걸리는 전압은 다음과 같은 식을 통해 구할 수 있다.

나머지는 앞서 구한 방법과 같다.

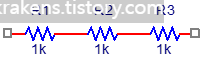

- 수동소자 연결

-직렬저항 : 직렬저항은 단순히 더해주면 된다.

Rt = R1 + R2 + R3 = 1k + 1k + 1k = 3k

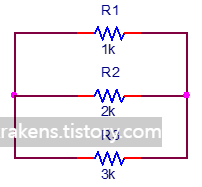

-병렬저항 : 병렬저항은 곱/덧 으로 볼 수 있다.

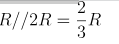

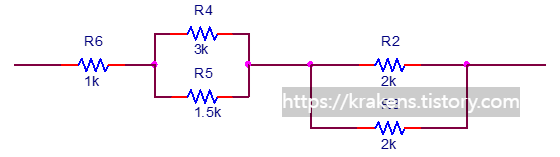

- 합성저항 계산

가장 윗 회로를 단순화 과정을 통해서 단순화를 끝냈다.

그 결과 3㏀계산 할 수 있었다.

- 과제

'[Harman] 하만 반도체 설계 > 전자회로' 카테고리의 다른 글

| Day40.RLC(공진)#2 (0) | 2023.09.06 |

|---|---|

| Day39.RLC(공진)#1 (0) | 2023.09.06 |

| Day38.인덕턴스 (0) | 2023.09.05 |

| Day 37.커패시턴스 (0) | 2023.09.05 |

| Day34. 전자회로 (KCL,KVL,등가회로) (0) | 2023.08.29 |