Kraklog

DAY10. Half Adder, Full Adder 본문

728x90

사용프로그램 : Cadence Virtuoso

Design Rule : Gpdk090

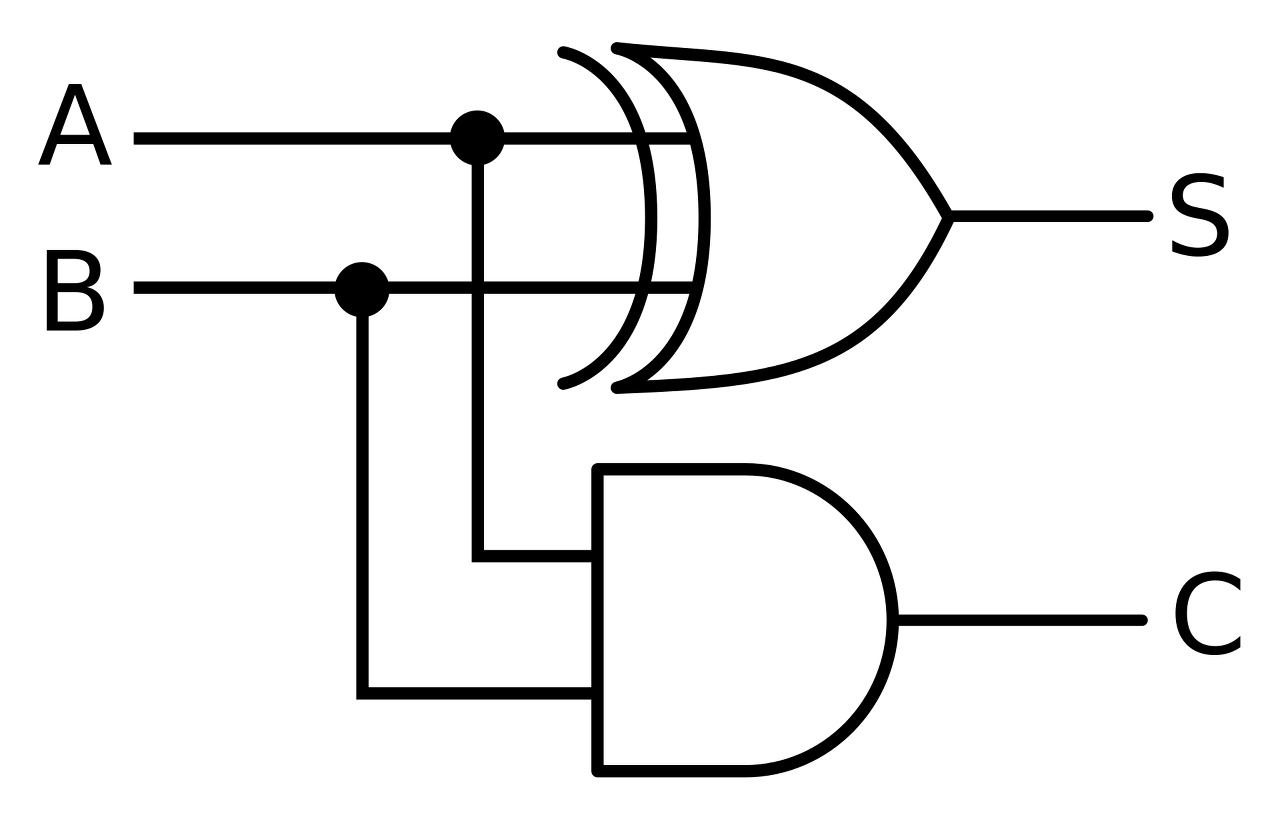

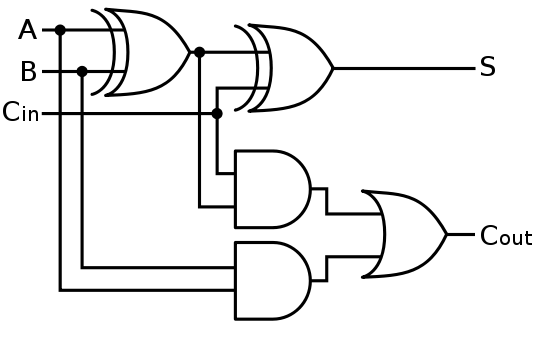

1. Half Adder 이론

- Schematic Diagram

조합논리회로는 출력이 이전의 입력에 관계없이 현재의 입력값에 의해 결정되는 논리회로이다.

조합논리 회로에는 반가산기, 전가산기, 반감산기,전감산기, 인코더,디코더, 멀티플렉서, 디멀티플렉서,비교기 등이 있다.

그 중 이번에는 가산기와 반가산기에 대해서 다뤄보았다.

-반가산기(HalfAdder)

반가산기란 1bit의 2진수 두 개를 덧셈한 Sum과 자리 올림수 Carry를 구하는 논리회로이다.

진리표에 따라 논리식을 구하면 다음과 같다.

논리식 :

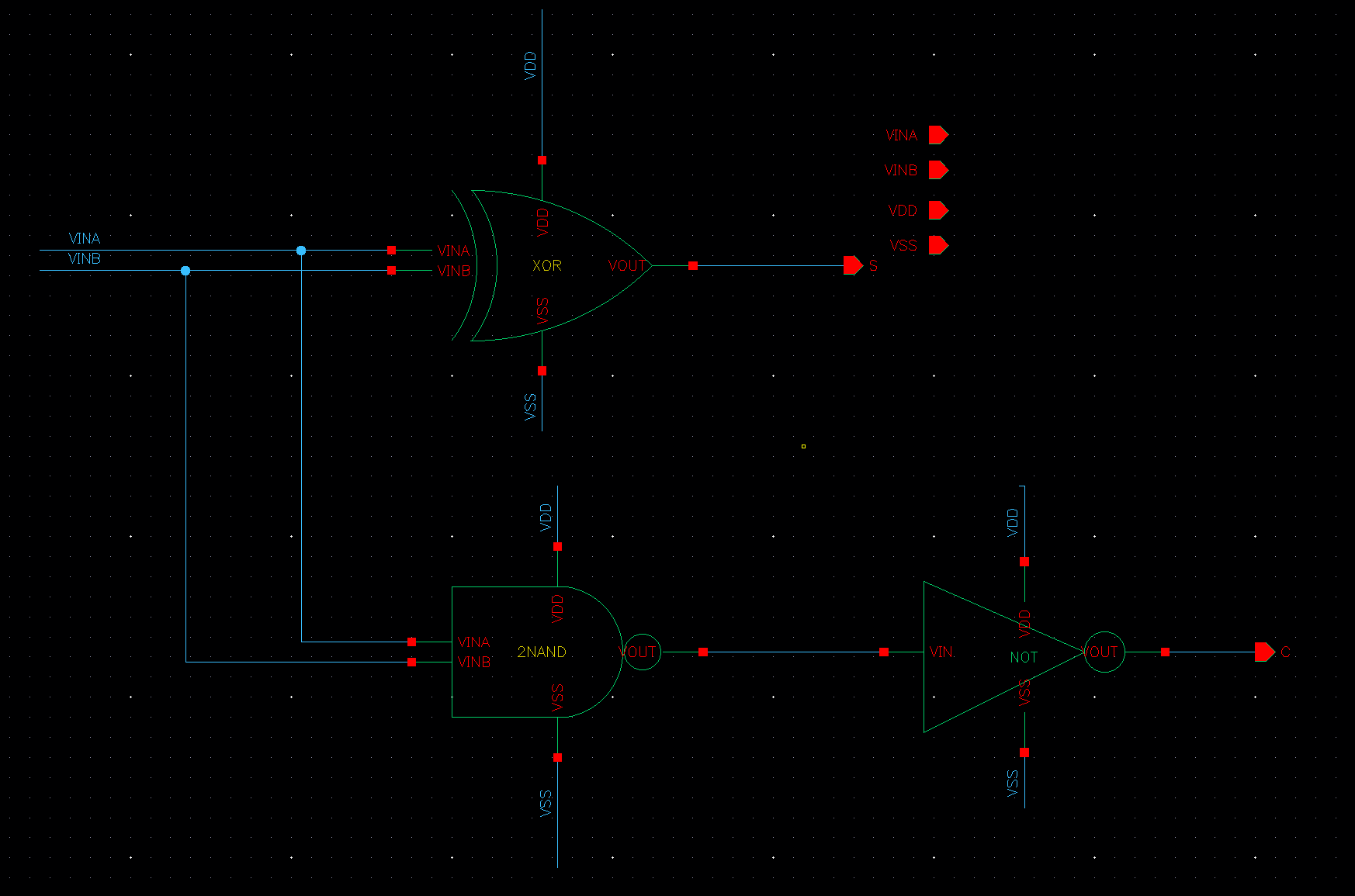

2. Design

- Schematic

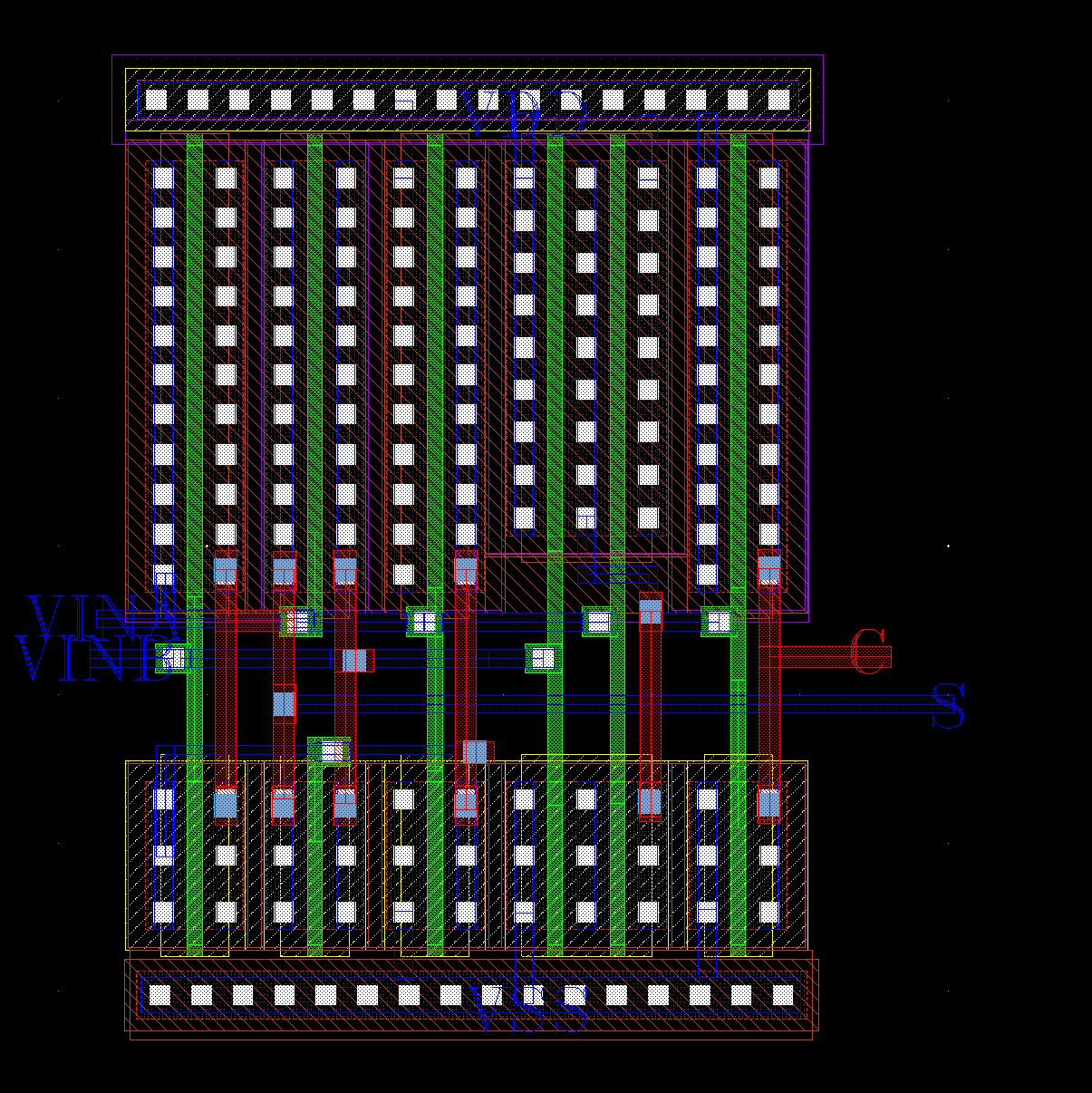

3. Layout

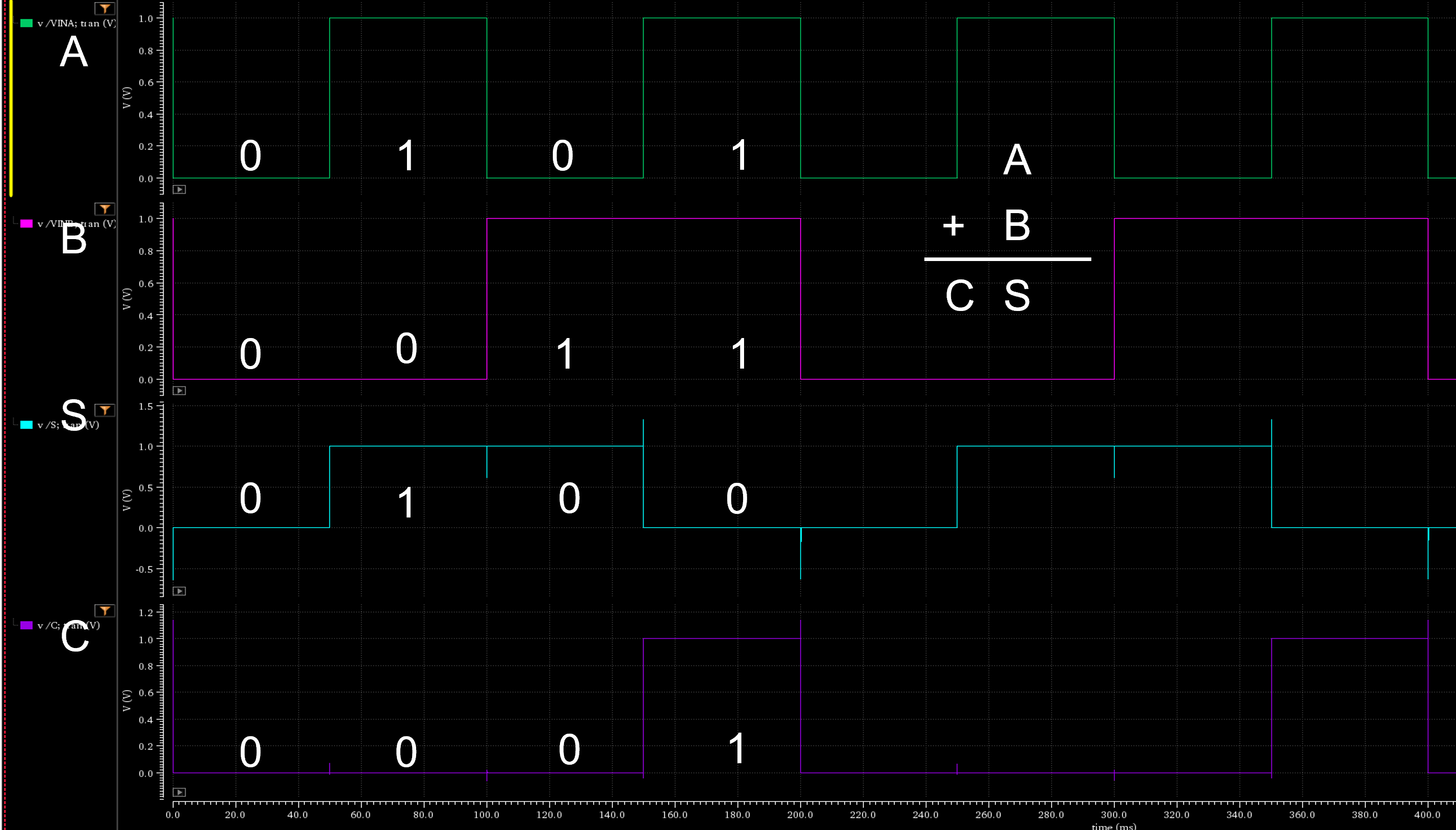

- Simulation

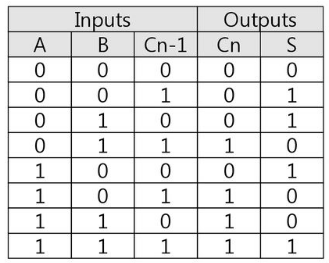

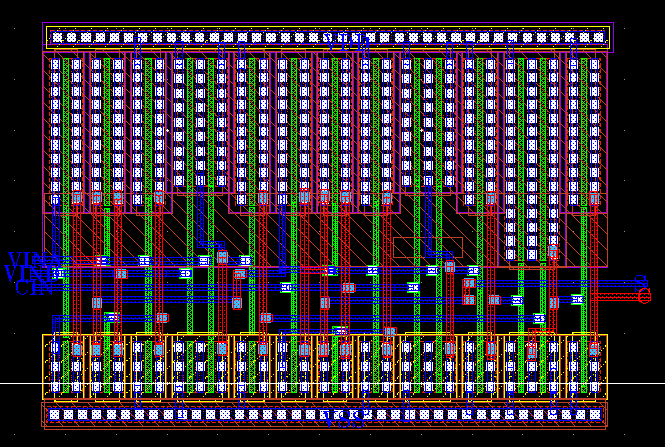

1. Full Adder 이론

- Schematic Diagram

전가산기는 반가산기와 달리 입력 값이 3개인데, 1bit 2진수 입력값 2개와, 뒷자리에서 올라온 Cin 으로 나뉘며,

출력은 Sum과 Carry(최종)로 나뉜다.

논리식 :

2. Design

- Schematic

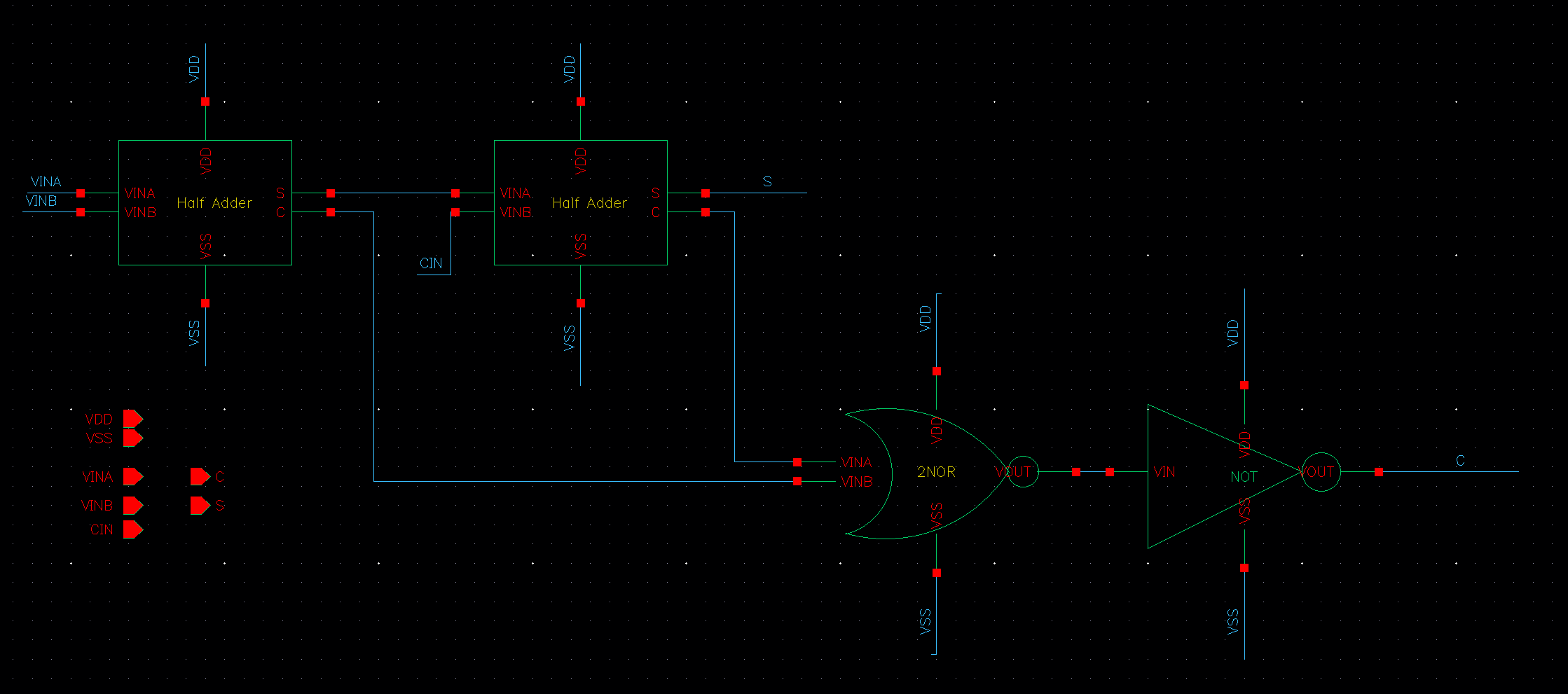

3. Layout

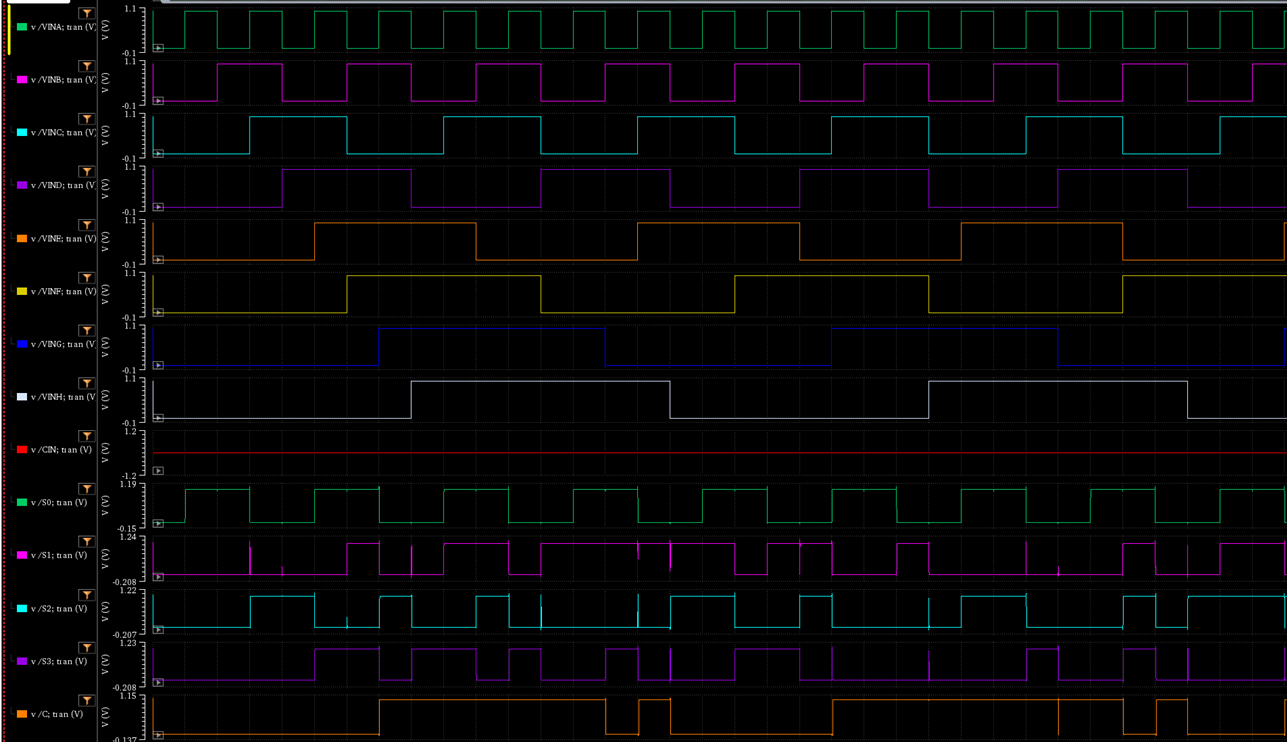

- Simulation

728x90

'[Harman] 하만 반도체 설계 > Full Custom One Chip' 카테고리의 다른 글

| DAY12. Analog Circuit (0) | 2023.07.18 |

|---|---|

| DAY11. 4Bit Adder / 4Bit Adder Substrate (4비트 가산기 감산기) (0) | 2023.07.18 |

| [하만]DAY8. 161MUX_SWITCH,161MUX_LOGIC 작성 (0) | 2023.07.15 |

| [하만]DAY7. 81MUX LOGIC,81MUX SWITCH (0) | 2023.07.12 |

| [하만]DAY6. 41MUX LOGIC,41MUX SWITCH (0) | 2023.07.12 |